### CONSIDERACIONES DE DISEÑO DEL PARALELISMO INTERNO EN HARDWARE A NIVEL DE INSTRUCCIÓN EN MICROPROCESADORES

**LUIS FERNANDO RUIZ JUAREZ**

ASESORADO POR: ING. GUSTAVO A. VILLEDA VÁSQUEZ

**GUATEMALA, OCTUBRE DE 2004**

#### UNIVERSIDAD DE SAN CARLOS DE GUATEMALA

### FACULTAD DE INGENIERÍA

## CONSIDERACIONES DE DISEÑO DEL PARALELISMO INTERNO EN HARDWARE A NIVEL DE INSTRUCCIÓN EN MICROPROCESADORES

TRABAJO DE GRADUACIÓN

PRESENTADO A JUNTA DIRECTIVA DE LA FACULTAD DE INGENIERÍA POR

**LUIS FERNANDO RUIZ JUÁREZ** ASESORADO POR: ING. GUSTAVO A. VILLEDA VÁSQUEZ

AL CONFERÍRSELE EL TÍTULO DE INGENIERO ELECTRÓNICO

GUATEMALA, OCTUBRE DE 2004

# UNIVERSIDAD DE SAN CARLOS DE GUATEMALA FACULTAD DE INGENIERÍA

### **NÓMINA DE JUNTA DIRECTIVA**

| DECANO     | Ing. Sydney Alexander Samuels Milson |

|------------|--------------------------------------|

| VOCAL I    | Ing. Murphy Olympo Paiz Recinos      |

| VOCAL II   | Lic. Amahán Sánchez Álvarez          |

| VOCAL III  | Ing. Julio David Galicia Celada      |

| VOCAL IV   | Br. Kenneth Issur Estrada Ruiz       |

| VOCAL V    | Br. Elisa Yazminda Vides Leiva       |

| SECRETARIO | Ing. Pedro Antonio Aguilar Polanco   |

### TRIBUNAL QUE PRACTICÓ EL EXAMEN GENERAL PRIVADO

| DECANO            | Ing. Sydney Alexander Samuels Milson |

|-------------------|--------------------------------------|

| <b>EXAMINADOR</b> | Ing. Luis Eduardo Durán Córdova      |

| EXAMINADOR        | Ing. Gustavo Adolfo Villeda Vásquez  |

| EXAMINADOR        | Ing. Francisco Javier González López |

| SECRETARIO        | Ing. Pedro Antonio Aguilar Polanco   |

|                   | <del>_</del>                         |

### HONORABLE TRIBUNAL EXAMINADOR

Cumpliendo con los preceptos que establece la ley de la Universidad de San Carlos de Guatemala, presento a su consideración mi trabajo de graduación titulado:

## CONSIDERACIONES DE DISEÑO DEL PARALELISMO INTERNO EN HARDWARE A NIVEL DE INSTRUCCIÓN EN MICROPROCESADORES

Tema que me fuera asignado por la Dirección de la Escuela de Ingeniería Mecánica Eléctrica, con fecha agosto de 2003.

Luis Fernando Ruiz Juárez

### **AGRADECIMIENTOS:**

A DIOS El alfa y la omega, Creador del Universo, mi aliento de

vida, merecedor de toda gloria y majestad.

A mis padres Por su apoyo diario y comprensión en cada etapa de

mi vida; le doy gracias a Dios por tenerlos y este paso

es algo que lo hemos logrado juntos.

A mis hermanos Gracias Manolo por tus consejos y por todos esos

momentos que los hemos pasado juntos. Gracias

Patty por tu compañía en todo momento.

A mis Tíos Por estar siempre al tanto, por preocuparse por mí y

por hacer posible la culminación de mi carrera.

A mis Primos Por compartir tantos momentos especiales en mi vida.

A mis compañeros

de universidad

Gracias a todos aquellos compañeros que en algún paso de mi vida me los encontré en mi carrera y que compartieron conmigo varios momentos inolvidables. Gracias Helmunt, Ferdi, Kenneth, Poncho, Edgar,

David, Ulises, Robin y a todos lo demás.

A mis catedráticos Les agradezco por haber contribuido en mi formación

profesional y en especial al Ing. Gustavo Villeda por sus consejos y su amistad brindada, y el apoyo para

poder desarrollar este trabajo de graduación.

A la universidad Gracias Universidad de San Carlos, gracias por darme

la dicha de pertenecer a un grupo selecto de profesionales, por lo que me esforzaré para colocar tu nombre en alto; sea el lugar donde me encuentre.

### **DEDICATORIAS:**

#### A Jesucristo

Por esa interseción divina que realizas día con día a la diestra del Padre y por el consuelo de tu Espíritu Santo, por ese toque que le dio vida a mi espíritu y que me hizo verte como una realidad, porque sin ti estaría perdido y nada de esto ni cualquier cosa del mundo valdría la pena.

#### A mi padre, Ing. José Luis Ruiz

Por todo ese conocimiento transmitido desde mis primeros días de estudio y por fomentarme a tener esa capacidad de análisis característica de todo buen ingeniero y sobre todo por tus consejos, apoyo y comprensión que me has proporcionado durante toda mi carrera.

#### A mi madre, Estelita

Tú has contribuido de gran manera en el desarrollo de mi carrera y has hecho la tarea de una madre ejemplar, estando presente en todo momento apoyándome incondicionalemente y siempre trantando de ayudarme, es por ello que formas una gran parte de este logro.

#### A mis hermanos, José Manuel y Silvia Patricia

Es un honor dedicarles este trabajo porque además de ser buenos hermanos, han sido buenos amigos y han sido parte de mi soporte para completar esta carrera, Dios los bendiga siempre.

#### A mis tíos, Mario y Flory

No solo les agradezco, sino que también les dedico este trabajo, por ser tan especiales y tan buenos conmigo en todo momento y por ser parte muy importante de este logro en mi vida.

### **ÍNDICE GENERAL**

| NDICE DE ILUSTRACIONES                                                        | v    |

|-------------------------------------------------------------------------------|------|

| ISTA DE SÍMBOLOS                                                              | ix   |

| BLOSARIO                                                                      | xi   |

| RESUMEN                                                                       | xvii |

| DBJETIVOS                                                                     | xix  |

| NTRODUCCIÓN                                                                   | xxi  |

| . CONCEPTOS GENERALES DEL PARALELISMO A NIVEL D<br>INSTRUCCIÓN ( <i>ILP</i> ) |      |

| 1.1. Condiciones de paralelismo                                               | 1    |

| 1.2. Dependencias entre instrucciones                                         | 4    |

| 1.2.1. Dependencias de datos                                                  | 5    |

| 1.2.1.1 Dependencias RAW (read after write)                                   | 6    |

| 1.2.1.2 Dependencias WAR (write after read)                                   | 8    |

| 1.2.1.3 Dependencias WAW (write after write)                                  | 9    |

| 1.2.2. Dependencias de control                                                | 10   |

| 1.2.3. Dependencias de recursos                                               | 11   |

| 1.3. Introducción al pipeline de instrucciones                                | 12   |

| 1.4. Paralelismo en software y paralelismo en hardware                        | 16   |

| 1.5. Conceptos de planificación de instrucciones                              | 20   |

| 1.5.1. Planificación dinámica                                                 | 22   |

| 1.5.2 Planificación estática                                                  | 25   |

| CONS  | SIDE                                                                        | RACIONES DE DISENO E IMPLEMENTACION                                                                                                                               |                                                              |

|-------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| DEL   | PIPE                                                                        | ELINE                                                                                                                                                             | 29                                                           |

| 2.1.  | Eta                                                                         | pas y registros del <i>pipeline</i>                                                                                                                               | 29                                                           |

| 2.2.  |                                                                             |                                                                                                                                                                   |                                                              |

| 2.3.  | Par                                                                         | adas debidas a dependencias (pipeline hazards)                                                                                                                    | 38                                                           |

| 2.3   | 1.                                                                          | Rendimiento del <i>pipeline</i> con paradas (stalls)                                                                                                              | 39                                                           |

| 2.3   | 2.                                                                          | Dependencias estructurales                                                                                                                                        | 40                                                           |

| 2.3   | .3.                                                                         | Dependencias de datos.                                                                                                                                            | 42                                                           |

| 2     | .3.3.                                                                       | 1 Minimización de paradas por medio de anticipación                                                                                                               |                                                              |

|       |                                                                             | (forwarding)                                                                                                                                                      | 44                                                           |

| 2.3   | 4.                                                                          | Dependencias de control (branch hazards)                                                                                                                          | 47                                                           |

| 2     | .3.4.                                                                       | 1 Reducción de las dependencias de ramificación                                                                                                                   | 49                                                           |

| 2.4.  | Mai                                                                         | nejo de excepciones (interrupciones y traps)                                                                                                                      | 54                                                           |

| 2.5.  | Ext                                                                         | ensión del <i>pipeline</i> para manipulación de                                                                                                                   |                                                              |

|       | ope                                                                         | eraciones multiciclo                                                                                                                                              | 59                                                           |

| 2.5   | 1.                                                                          | Dependencias y anticipación en pipelines de gran latencia                                                                                                         | 61                                                           |

| 2.5   | 2.                                                                          | Tratamiento preciso de excepciones                                                                                                                                | 63                                                           |

| CONS  | SIDE                                                                        | RACIONES DE DISEÑO EN LA PLANIFICACIÓN DINÁMICA                                                                                                                   | DE                                                           |

| INSTI | RUC                                                                         | CIONES                                                                                                                                                            | 67                                                           |

| 3 1   | Pla                                                                         | nificación dinámica del <i>nineline</i> (scoreboarding)                                                                                                           | 68                                                           |

|       |                                                                             |                                                                                                                                                                   |                                                              |

|       |                                                                             | -                                                                                                                                                                 |                                                              |

|       |                                                                             | •                                                                                                                                                                 |                                                              |

|       |                                                                             |                                                                                                                                                                   |                                                              |

|       |                                                                             |                                                                                                                                                                   |                                                              |

|       |                                                                             | Branch-target Buffers                                                                                                                                             |                                                              |

|       | 2.1. 2.2. 2.3. 2.3. 2.3. 2.3. 2.3. 2.4. 2.5.  CONSINSTI 3.1. 3.2. 3.3. 3.4. | 2.1. Eta 2.2. Ecu 2.3. Par 2.3.1. 2.3.2. 2.3.3. 2.3.4. 2.3.4. 2.3.4. 2.4. Ma 2.5. Ext ope 2.5.1. 2.5.2.  CONSIDE INSTRUC 3.1. Pla 3.2. Pla 3.3. Rec 3.3.1. 3.3.1. | <ul> <li>2.2. Ecuación de rendimiento del pipeline</li></ul> |

|   | 3.4.2  | 2. Uni    | dades IF integradas                                 | 90  |

|---|--------|-----------|-----------------------------------------------------|-----|

|   | 3.4.3  | 3. Ret    | urn Address Predictors                              | 91  |

|   | 3.5.   | Ejecució  | n especulativa basada en <i>hardware</i>            | 92  |

|   | 3.5.   | 1. Cor    | nsideraciones de diseño                             | 98  |

|   | 3.     | 5.1.1     | Renombre de registros                               | 98  |

|   | 3.     | 5.1.2     | Especulación a través de múltiples ramificaciones   | 102 |

| 4 | . CONS | SIDERAC   | IONES DE DISEÑO GENERALES EN BASE A                 |     |

| • |        |           | S DEL ILP EN HARDWARE                               | 105 |

|   | 4.1.   | Conside   | raciones respecto al modelo de hardware             | 105 |

|   | 4.2.   | Limitacio | ones en el tamaño de ventana                        | 107 |

|   | 4.3.   | Efectos   | en la predicción de saltos y ramificaciones reales  | 109 |

|   | 4.4.   | Los efec  | ctos de registros finitos                           | 112 |

|   | 4.5.   | Limitacio | ones del ILP para procesadores realizables          | 113 |

| 5 | . HERR | AMIENT    | AS DE SIMULACIÓN COMO                               |     |

| • |        |           | L DISEÑO                                            | 119 |

|   | 5.1.   | Concept   | os generales de simuladores utilizados              | 119 |

|   | 5.1.   | 1. Tipo   | os de simuladores                                   | 120 |

|   | 5.     | 1.1.1     | Simuladores de modelo estático (static modeling)    | 122 |

|   | 5.     | 1.1.2     | Simuladores dirigidos mediante trazas               |     |

|   |        |           | (trace-driven simulation)                           | 123 |

|   | 5.     | 1.1.3     | Execution-driven simulators                         | 125 |

|   | 5.     | 1.1.4     | Análisis comparativo de las técnicas de simulación. | 125 |

|   | 5.2.   | Descripe  | ción de algunos simuladores                         | 126 |

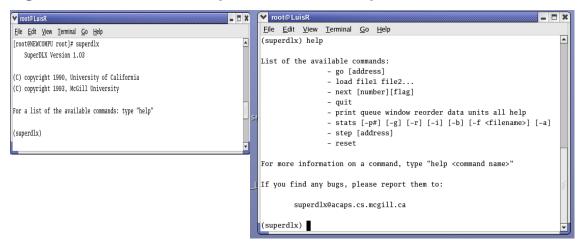

|   | 5.2.   | 1. Win    | dlx (Windows Deluxe Simulator)                      | 127 |

|   | 5.2.2  | 2. Win    | mips64                                              | 132 |

| 5.2.3.          | Dlxview                                                 | 135      |  |

|-----------------|---------------------------------------------------------|----------|--|

| 5.2.3.          | 1 Simulación del <i>pipeline</i> básico                 | 137      |  |

| 5.2.3.          | 2 Simulación de planificación dinámica de instrucciones | <b>;</b> |  |

|                 | mediante el algoritmo de Tomasulo                       | 141      |  |

| 5.2.3.          | 3 Simulación de scoreboarding                           | 143      |  |

| 5.2.3.          | 4 Superscalar (Superdlx)                                | 145      |  |

|                 |                                                         |          |  |

| CONCLUSIONES1   |                                                         |          |  |

| RECOMENDACIONES |                                                         |          |  |

| RIRI IOGRA      | RIBLIOGRAFÍA 156                                        |          |  |

### **ÍNDICE DE ILUSTRACIONES**

### **FIGURAS**

| 1.  | Elementos presentes en el procesamiento de una instrucción            | 1  |

|-----|-----------------------------------------------------------------------|----|

| 2.  | Ejecución secuencial y ejecución paralela de instrucciones            | 3  |

| 3.  | Clasificación de las dependencias de datos                            | 6  |

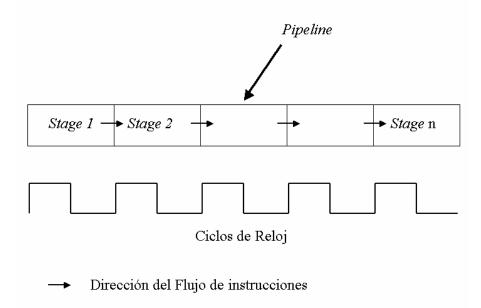

| 4.  | Organización de los estados del <i>pipeline</i> en función del tiempo | 13 |

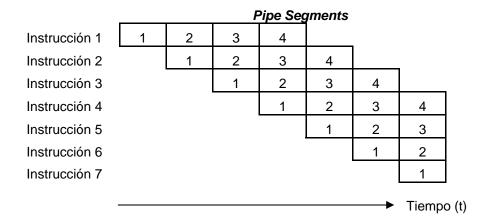

| 5.  | Segmentación de instrucciones y su ejecución                          | 15 |

| 6.  | Paralelismo en hardware y paralelismo en software                     | 18 |

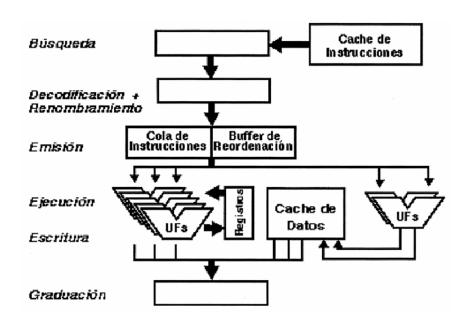

| 7.  | Organización típica de un procesador superescalar                     | 23 |

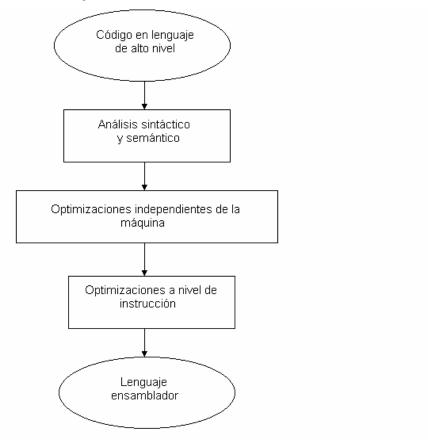

| 8.  | El proceso de compilación                                             | 26 |

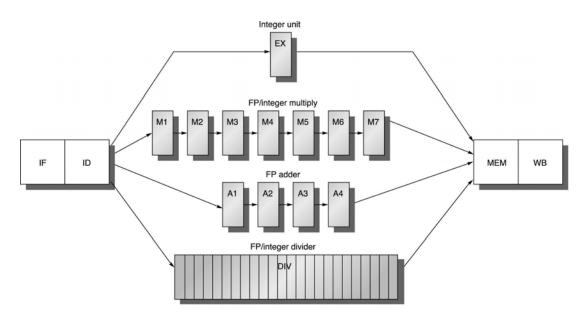

| 9.  | Unidades funcionales en el pipeline                                   | 33 |

| 10. | Conflicto en el acceso a memoria, debido a                            |    |

|     | dependencias estructurales                                            | 41 |

| 11. | Obstáculos en el pipeline debido a dependencias de datos              | 43 |

| 12. | Utilización de la técnica de anticipación (forwarding)                | 44 |

| 13. | Dependencia de datos de una instrucción de carga                      | 46 |

| 14. | Secuenciamiento implícito.                                            | 47 |

| 15. | Planificación del delay slot.                                         | 53 |

| 16. | Estructura del pipeline con 3 unidades funcionales de punto flotante  | 60 |

| 17. | Etapa de ejecución multiciclo parcialmente segmentada                 | 61 |

| 18. | Estructura básica de un procesador con scoreboard                     | 71 |

| 19. | Estructura de unidad de punto flotante utilizando                     |    |

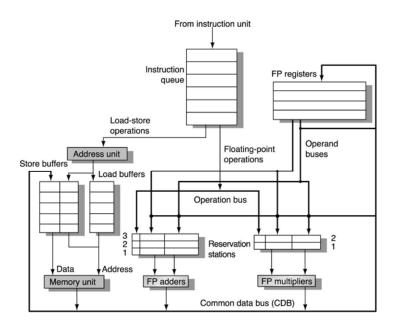

|     | el algoritmo de Tomasulo                                              | 73 |

| 20. | Detalle del algoritmo de Tomasulo                                     | 76 |

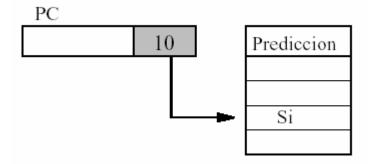

| 21. | Acceso mediante una porción del PC al buffer de predicción                 | .78 |

|-----|----------------------------------------------------------------------------|-----|

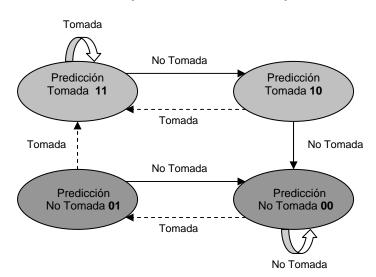

| 22. | Estados en un esquema con 2 bits de predicción                             | .80 |

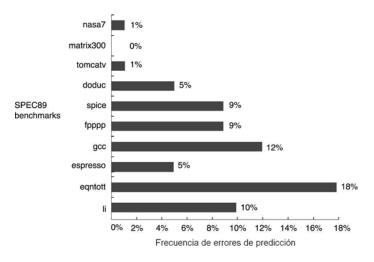

| 23. | Precisión de predicción para un búfer de 4096 entradas y dos bits por      |     |

|     | entrada                                                                    | .81 |

| 24. | Comparación de un búfer de predicción de 2 bits con 4096 entradas y un     | 0   |

|     | de entradas ilimitadas                                                     | .82 |

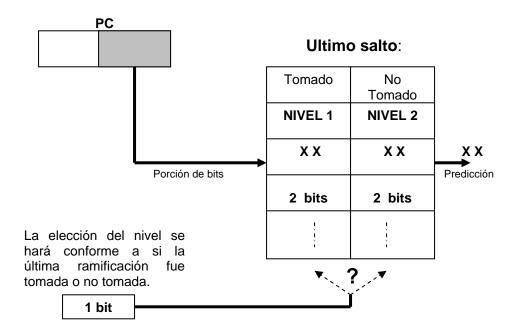

| 25. | Predictor (1,2) que utiliza el comportamiento del último salto             | .84 |

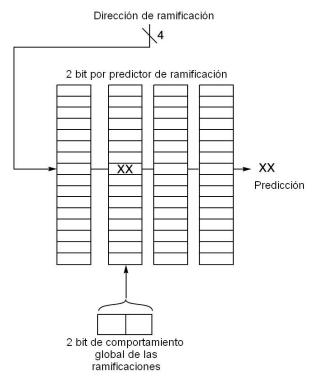

| 26. | Predictor correlacionado utilizando 2 bits de historia global para escoger | 4   |

|     | predictores para cada dirección de ramificación.                           | .85 |

| 27. | Comparación entre predictores de 2 bits                                    | .86 |

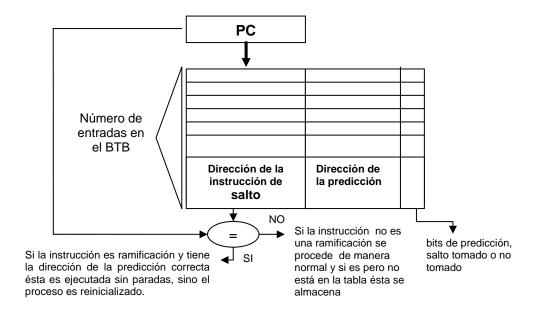

| 28. | Estructura de un branch target buffer (BTB)                                | .88 |

| 29. | Pasos involucrados en la manipulación de una instrucción con un BTB        | .89 |

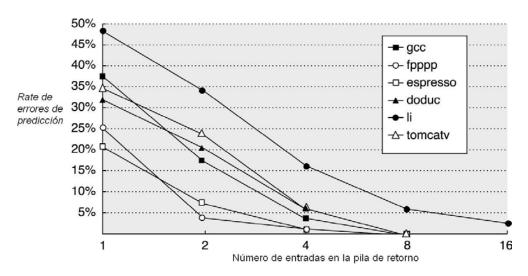

| 30. | Precisión de predicción para un return address predictor operando como     |     |

|     | pila                                                                       | .92 |

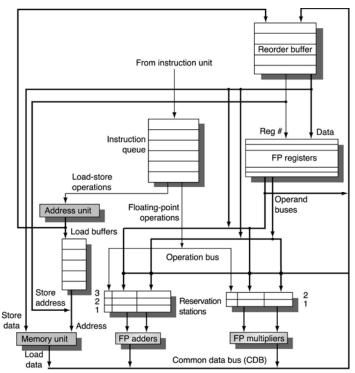

| 31. | Estructura básica de una unidad de punto flotante usando el algoritmo de   | )   |

|     | Tomasulo especulativo                                                      | .96 |

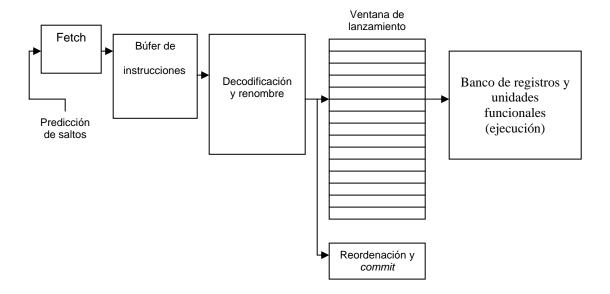

| 32. | Diagrama de bloques general del proceso de emisión y ejecución de          |     |

|     | instrucciones                                                              | 107 |

| 33. | Efecto de diferentes esquemas de predicción                                | 109 |

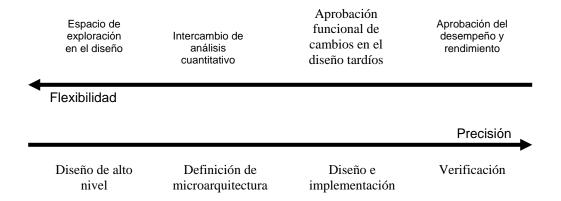

| 34. | Utilización de la simulación durante el proceso de diseño                  | 121 |

| 35. | Ventana de <i>pipeline</i> en el simulador Windlx                          | 127 |

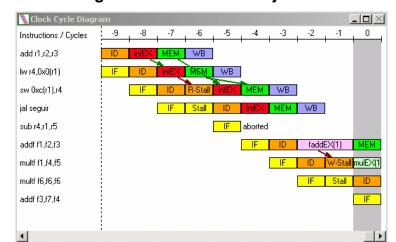

| 36. | Ventana del diagrama de ciclos de reloj del simulador Windlx               | 128 |

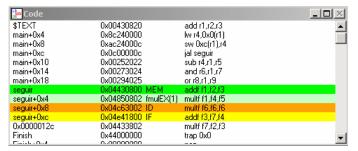

| 37. | Ventana de código del simulador Windlx                                     | 129 |

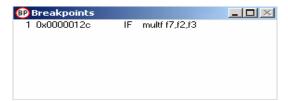

| 38. | Ventana de breakpoints en el simulador Windlx                              | 129 |

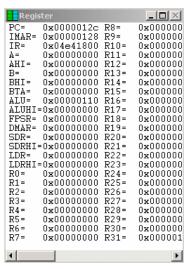

| 39. | Ventana de registros del simulador Windlx                                  | 130 |

| 40. | Ventana de estadísticas del Windlx                                         | 131 |

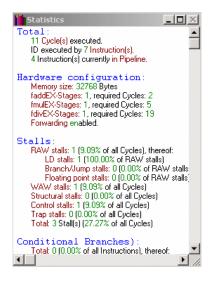

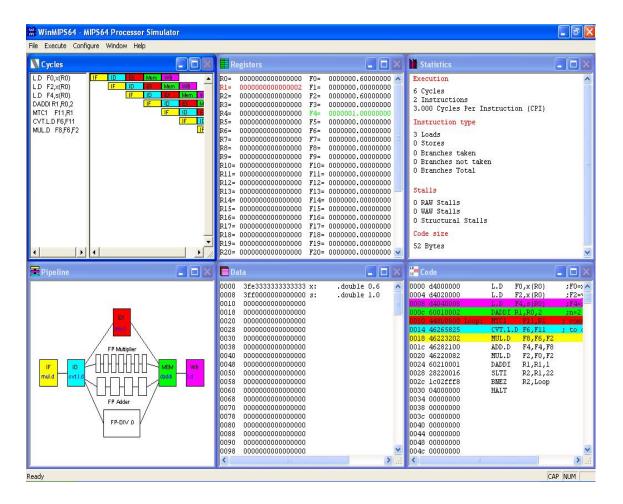

| 41. | Interfaz gráfica del simulador Winmips64                                   | 133 |

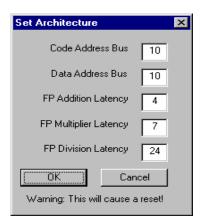

| 42. | Ventana de configuración de arquitectura del simulador Winmips64 1         | 134 |

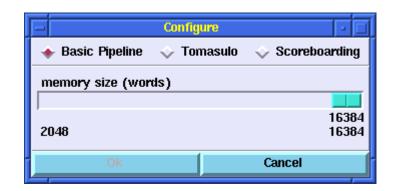

| 43.         | Ventana de configuración de memoria y modo de operación en el           |     |

|-------------|-------------------------------------------------------------------------|-----|

|             | simulador DlxView 0.9.                                                  | 137 |

| 44.         | Ventana de configuración del pipeline básico en el simulador            | 137 |

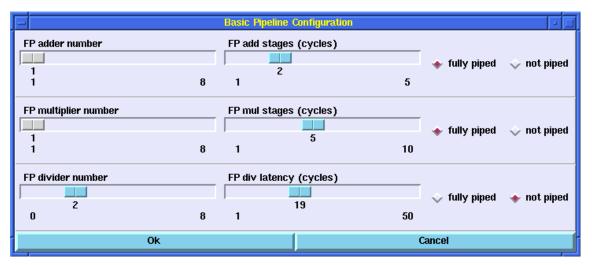

| 45.         | Ventana de control del simulador Dixview.                               | 138 |

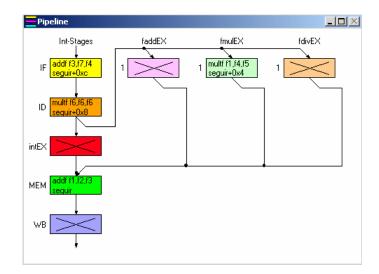

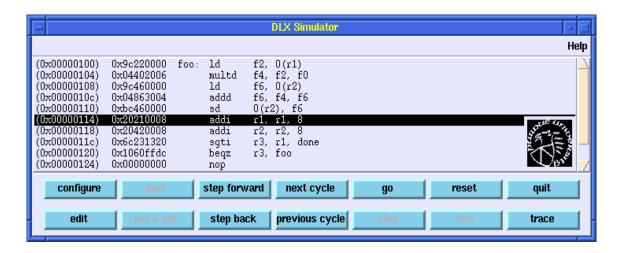

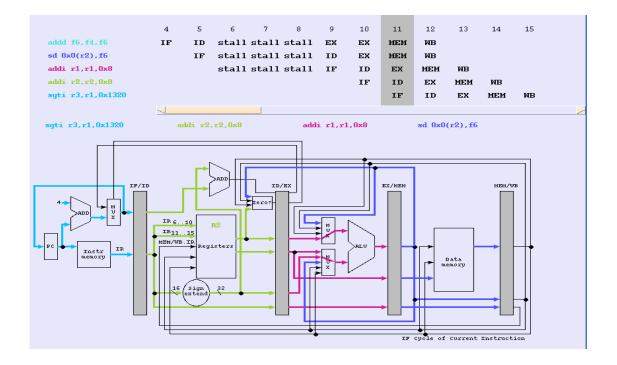

| 46.         | Ventana del <i>pipeline</i> básico en el simulador Dlxview              | 139 |

| <b>47</b> . | Ventana del flujos de datos en la unidad entera del <i>pipeline</i> del | 140 |

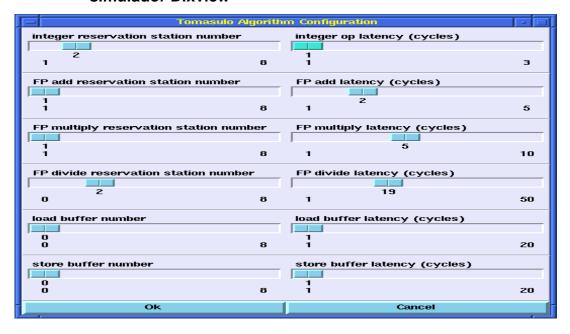

| 48.         | Ventana de configuración del algoritmo de Tomasulo                      | 142 |

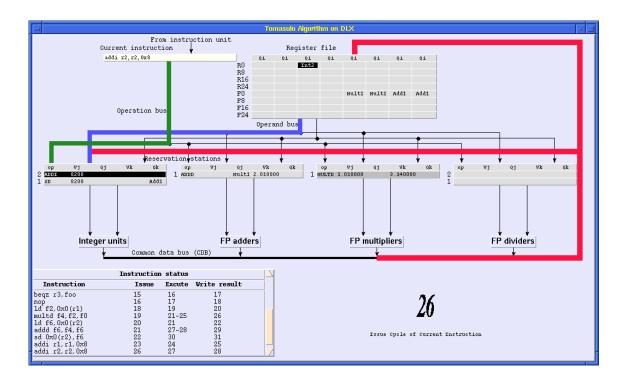

| 49.         | Ventana de flujo del algoritmo de Tomasulo en el simulador              | 142 |

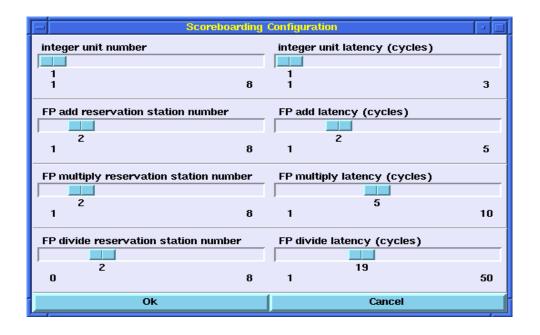

| <b>50</b> . | Ventanta de configuración del scoreboarding de Dlxview                  | 143 |

| 51.         | Ventana de ejecución del algoritmo del scoreboarding de Dlxview         | 144 |

| <b>52.</b>  | Ambiente en el que se desarrolla Superdlx                               | 145 |

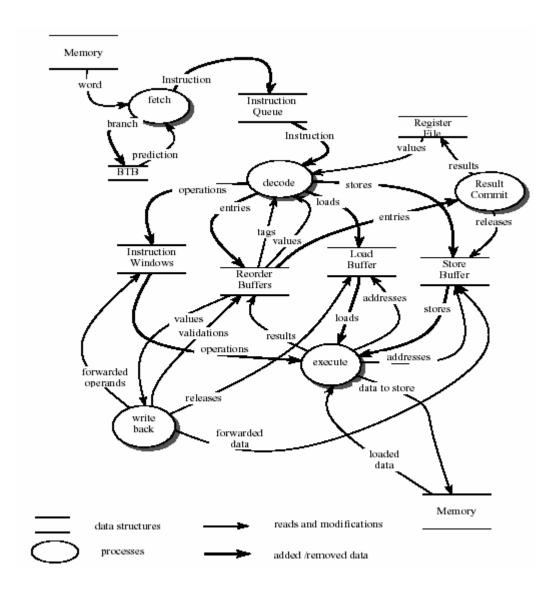

| 53.         | Modelo de procesador superescalar utilizado por Superdlx                | 146 |

| 54.         | Funcionamiento global del manejo de instrucciones de Superdlx           | 147 |

### **TABLAS**

| I.    | Tipos de planificación                                                 | 20  |

|-------|------------------------------------------------------------------------|-----|

| II.   | Características principales de las diferentes arquitecturas de         |     |

|       | microprocesadores y algunos ejemplos.                                  | 21  |

| III.  | Estrategias de emisión de instrucciones utilizadas en la planificación |     |

|       | dinámica                                                               | 25  |

| IV.   | Pipeline básico.                                                       | 32  |

| ٧.    | Parada debida a dependencia estructural                                | 42  |

| VI.   | Paradas causadas por la dependencia de datos de una instrucción de     |     |

|       | carga                                                                  | 47  |

| VII.  | Parada de un ciclo debido a una ramificación                           | 48  |

| VIII. | Esquema de toma de ramificación                                        | 50  |

| IX.   | Comportamiento del pipeline con esquema delayed branch                 | 52  |

| Χ.    | Acciones necesitadas para diferentes tipos de excepciones              | 57  |

| XI.   | Marcador de estado de las instrucciones                                | 69  |

| XII.  | Marcador de estado de las unidades funcionales                         | 70  |

| XIII. | Marcador de estado de escritura a registros                            | 70  |

| XIV.  | . Características de hardware de procesadores de los últimos años      | 116 |

| XV.   | Atributos de varias técnicas de simulación                             | 126 |

### **LISTA DE SÍMBOLOS**

IIParalelismo Transferencia de datos de una fuente almacenamiento a otra Transferencia de resultado de una operación Intersección entre el uso elementos de diferentes  $\cap$ procesos { .... } Cuerpo del programa **CDB** Bus de datos común entre unidades funcionales **CPI** Ciclos de reloj por instrucción Gigahertz **GHz ILP** Paralelismo a nivel de instrucción Nanosegundos Ns Promedio de ejecución paralela **PEP** Unidad funcional UF

CONSIDERACIONDES DE DISEÑO DEL PARALELISMO INTERNO EN HARDWARE A NIVEL DE INSTRUCCIÓN EN MICROPROCESADORES

### **GLOSARIO**

**ALU** Unidad encargada de realizar operaciones del tipo

aritmético-lógicas.

Amdahl Ley utilizada para calcular la ganancia del

rendimiento debido al perfeccionamiento de alguna

porción de la arquitectura.

Antidependencia Dependencia causada por la reutilización del nombre

de un registro, también llamada dependencia falsa,

correspondiente a los riesgos del tipo WAR y WAW.

Average Promedio de instrucciones realizadas por unidad de

tiempo.

**Benchmark** Software utilizado para medir el rendimiento de un

sistema. Algunos de los benchmarks están

especialmente diseñados para probar áreas

específicas de un sistema, mientras que otros son

usados para ejecutar múltiples pruebas y dar un

índice de calidad general del rendimiento medido.

Branch delay slot Espacio destinado para una instrucción, donde la

instrucción es ejecutada independientemente si la

ramificación es tomada o no, utilizado en la técnica

de branch delay.

Cache Memoria de rápido acceso, basada en el principio de

localidad.

Commit Proceso clave en la implementación de la

especulación de instrucciones, permitiendo que las instrucciones sean ejecutadas fuera de orden pero

forzando a que sean entregadas en orden y prevenir

cualquier acción irrevocable.

Compilador Software encargado de llevar el código de un

lenguaje de alto nivel a lenguaje ensamblador,

mediante un análisis sintáctico y semántico.

Estación de reserva Estaciones encargadas de almacenar las

instrucciones que están pendientes de entrar a una

unidad funcional.

**Excepción** Correspondiente a cualquier tipo de interrupción

ocurrida en el flujo normal de instrucciones.

Fetch Etapa en el procesamiento de la instrucción donde

ésta es extraída de la memoria. Corresponde al

estado IF (*Instruction Fetch*) del *pipeline*.

**Forwarding** Técnica de paralelismo basada en la anticipación con

el objeto de minimizar paradas en el pipeline,

también conocida como bypassing ó shorcircuiting.

Hardware Correspondiente a toda circuitería física interna del

microprocesador.

Hyperpipeline Tecnología basada en el principio de pipeline la cual

esta constituída de un gran número de estados o

etapas en el procesamiento de instrucciones.

Idle Estado inactivo en el flujo de instrucciones.

PC (Program Registro encargado de almacenar la dirección de

**Counter)** memoria correspondiente a la instrucción a ejecutar.

Pipeline Técnica de paralelismo, basada en la segmentación

del proceso de ejecución de instrucciones,

permitiendo que diferentes estados de varias

instrucciones sean ejecutados al mismo tiempo.

Pipeline interlock Hardware encargado de la detección de las

dependencias en el pipeline, capaz de provocar una

parada hasta que la dependencia sea eliminada.

Planificación Planificación realizada mediante hardware en tiempo

dinámica de ejecución a través de múltiples instrucciones.

Planificación estática Planificación realizada mediante el proceso de

compilación con el objeto de optimizar el código para

su ejecución, reduciendo la cantidad de hardware,

respaldándose; sin embargo, en técnicas

correspondientes a la planificación dinámica.

Principio de Principio basado en el hecho de que varios

Localidad

programas tienden a reutilizar datos e instrucciones

que fueron utilizados recientemente.

Rate Inverso del tiempo de ciclo de reloj, usualmente

medido en hertz.

RAW (Read After

Write)

Dependencia de datos que produce el riesgo la lectura a una fuente antes de que la instrucción

predecesora escriba a ésta.

**ROB** Búfer de reordenamiento que mantiene el resultado

de las instrucciones que han finalizado su ejecución

pero no han llevado a cabo el proceso de commit.

**Scoreboarding** Técnica de paralelismo basada en el uso de un

marcador de control, por medio del cual es posible

realizar una ejecución especulativa.

Simulación Herramienta básica en muchos campos de la ciencia

y la ingeniería, para complementar (y a veces,

sustituir) a otras técnicas como el estudio analítico y

el desarrollo de prototipos.

**Speedup** Aumento del rendimiento al utilizar una característica

adicional en nuestro sistema.

**Stall** Parada en el flujo del *pipeline* debida a

dependencias.

Superescalar Procesador capaz de ejecutar múltiples instrucciones

por ciclo de reloj con emisión de instrucciones

controlada dinámicamente por hardware.

**Tomasulo**

Algoritmo basado en la técnica de scoreboarding teniendo como gran ventaja el uso de renombramiento de registros. Lleva el nombre en honor a Robert Tomasulo quien lo implemento por primera vez en el procesador IBM 360.

Traza

Describe la forma, orden y secuencia en que diferentes elementos (instrucciones, datos y direcciones) son tratados en determinado proceso, para hacer posible la simulación.

Unidad functional (UF)

Unidades destinadas a una función especifica en el proceso de ejecución de instrucciones.

VLIW

Procesador que ejecuta múltiples instrucciones por ciclo de reloj con emisión de instrucciónes controlada estáticamente mediante *software*.

WAR (Write After Read)

Dependencia de datos que produce el riesgo de la escritura a un destino determinado antes de que sea leído por la instrucción predecesora.

WAW (Write After Write)

Dependencia de datos que produce el riesgo de la escritura a un operando antes de que la instrucción predecesora escriba éste.

Wire delay

Retardo de una señal en una línea conductiva

CONSIDERACIONDES DE DISEÑO DEL PARALELISMO INTERNO EN HARDWARE A NIVEL DE INSTRUCCIÓN EN MICROPROCESADORES

### RESUMEN

Este trabajo de graduación presenta una serie de consideraciones de los aspectos más relevantes empleados en el diseño de paralelismo a nivel de instrucción (ILP) basado en *hardware* dentro de las arquitecturas de microprocesadores empleados en los últimos años, mostrando las opciones utilizadas para emplear al máximo las ventajas que ofrece el ILP y las limitantes a las que está sometido.

El primer capítulo describe un panorama general de las diferentes ventajas, obstáculos y herramientas existentes en la implementación del ILP y la necesidad de implementación; también presenta una introducción a los diferentes tipos de planificación empleados.

El segundo capítulo describe la técnica de *pipeline* utilizada actualmente en cualquier procesador, describiendo sus etapas básicas en cuanto a segmentación, enfatizando en la afección positiva al rendimiento que esta técnica posee y la influencia que existe de obstáculos presentados por medio de dependencias, tanto estructurales como dependencias entre instrucciones. Además, se desarrolla la interdependencia del *pipeline* respecto al manejo de excepciones y operaciones de punto flotante, presentando a lo largo del capítulo, limitantes y soluciones alternativas de acuerdo con los problemas presentados en el diseño de esta técnica.

El tercer capítulo desarrolla el enfoque requerido al planificar dinámicamente el ILP para emitir instrucciones múltiples a pesar de las dependencias que se presenten, empezando el desarrollo desde la técnica básica de *scoreboarding* para luego tratar la técnica ya perfeccionada: el algoritmo de Tomasulo. En éste se introduce la técnica de renombramiento de registros, creando entonces, el concepto de rastrear y procesar las dependencias en instrucciones para permitir la ejecución tan pronto como los operandos estén disponibles y un renombramiento de registros para eliminar las dependencias, siendo lo anterior la clave del procesamiento de diferentes microprocesadores actuales. Posteriormente, se trata sobre herramientas de predicción, permitiendo de esta manera completar el proceso de especulación de instrucciones presentando a la vez varias consideraciones de diseño.

El cuarto capítulo abarca desde un punto de vista general las consideraciones en el diseño de cualquier arquitectura que tenga como base el ILP en *hardware*, enfatizando en este limitantes tecnológicas; además incluye un estudio sobre los logros e impedimentos en el desarrollo de microprocesadores realizables.

El último capítulo describe la simulación como una herramienta útil en el transcurso de las diferentes etapas del diseño, y toma en consideración la relación flexibilidad-precisión. Luego de ello, a lo largo del capítulo, se describen diferentes simuladores que hacen posible desarrollar conceptos básicos de diseño y estudio del comportamiento respecto a la capacidad de las diferentes técnicas utilizadas en el ILP.

### **OBJETIVOS**

#### General

Desarrollar las consideraciones de diseño necesarias del paralelismo interno en *hardware* a nivel de instrucción en microprocesadores.

### Específicos

- Mostrar un panorama general del desarrollo del paralelismo a nivel de instrucción, para enmarcar correctamente, el diseño del paralelismo en hardware.

- Desarrollar las consideraciones de diseño necesarias en la implementación de *pipeline*, respecto a los diferentes procesos que se ven involucrados, su estructura, así como conocer sus limitaciones.

- 3. Desarrollar consideraciones de diseño en el momento de planificar dinámicamente las instrucciones respecto a los diferentes procesos implicados, algoritmos, elementos de *hardware*, así como describir algunas de las limitaciones de dicha planificación.

- 4. Desarrollar consideraciones de diseño generales respecto a limitaciones, implícitas en el paralelismo en *hardware* a nivel de instrucción.

- 5. Presentar diferentes herramientas de simulación, útiles para el diseño y estudio del comportamiento ante diferentes situaciones que se presentan en algunas de las técnicas utilizadas en el paralelismo en hardware a nivel de instrucción.

### INTRODUCCIÓN

Una de las tendencias actuales en el diseño de microprocesadores consiste en la ejecución de instrucciones en paralelo de una manera segmentada (*pipeline*), mediante la implementación del procesamiento fuera de orden utilizando técnicas de predicción, especulación y renombramiento de registros, formando la base de una planificación dinámica.

La planificación dinámica es implementada en la microarquitectura por medio de *hardware* mediante el uso de varias unidades funcionales, estaciones de reserva, bancos de registros y un sinnúmero de búfers y registros intermedios, permitiendo así el mejor aprovechamiento del tiempo, realizando una ejecución en paralelo, sólo tiene en cuenta la disponibilidad de datos y recursos sin tomar el orden del programa.

Uno de los grandes obstáculos para el desarrollo del paralelismo a nivel de instrucción (ILP) por medio de la planificación dinámica, surge de las dependencias entre instrucciones en lo correspondiente a operandos y el control de ramificaciones, además de límites tecnológicos como consecuencia de la miniaturización y consumo de potencia, agregando a esto dependencias estructurales debidas a la cantidad de *hardware* disponible. Son varias las limitantes existentes, así como las soluciones que se han ido desarrollando a través de los años permitiendo la manifestación de diferentes modelos de *hardware*, con ello se debe tomar en cuenta aspectos relacionados con el desarrollo y evaluación para un diseño en particular.

En este documento se exponen varias consideraciones de diseño con base en cualidades de las diferentes técnicas de ILP existentes respecto a *hardware* y en algunas oportunidades se elabora un análisis cuantitativo de acuerdo con resultados obtenidos por medio *software* de evaluación (*benchmarks*); al final la simulación se muestra como una herramienta auxiliar en el diseño.

# 1. CONCEPTOS GENERALES DEL PARALELISMO A NIVEL DE INSTRUCCIÓN (*ILP*)

#### 1.1. Condiciones de paralelismo

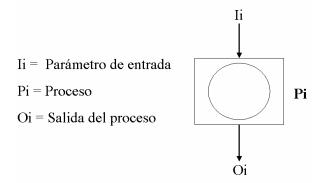

Una de las formas más efectivas para mejorar el desempeño de los microprocesadores es la implementación de técnicas de *hardware* y *software* que permitan la ejecución de más de una instrucción en paralelo durante un sólo ciclo de máquina. Las condiciones necesarias para satisfacer lo expuesto, son los principios de las técnicas de paralelismo implementadas en los microprocesadores. Al analizar el paralelismo a nivel de instrucción, es necesario determinar los diferentes elementos, a los que está sujeto el procesamiento de una instrucción, tal como se muestra en la figura 1.

Figura 1. Elementos presentes en el procesamiento de una instrucción

Todo proceso *Pi* necesita parámetros de entrada, cuyo conjunto denotaremos por *li*, éstos parámetros de entrada representan los valores de las variables de entrada relacionadas al proceso. Sin estas variables no es posible que el microprocesador realice su tarea fundamental que es procesar datos. Adicionalmente, la ejecución del proceso genera valores de salida, los cuales son escritos en los registros de propósito general del *CPU*, posiciones de memoria o puertos. Estos valores corresponden a las variables de salida del proceso *Pi* cuyo conjunto denotaremos por *Oi*. Esto implica que los valores de entrada de un proceso denominado *P1* no dependan de los valores de salida de un proceso *P2*, y que los valores de entrada del proceso *P2* no dependan de los valores de salida del proceso *P1* y *P2* no dependan entre sí, es decir:

$$11 \cap O2 = 0$$

$$12 \cap O1 = 0$$

$$O1 \cap O2 = 0$$

Para que dos o más procesos puedan ser ejecutados en paralelo deben cumplirse las tres condiciones expuestas anteriormente. Cuando esto ocurre se dice que los procesos *P1* y *P2* pueden ser ejecutados en paralelo, lo cual se denota por *P1||P2*.

Para demostrar la función de los principios antes expuestos en un sistema microprocesado, analicemos el diagrama de interdependencia de procesos que se presenta en la figura 2.

Figura 2. Ejecución secuencial y ejecución paralela de instrucciones

Este diagrama de interdependencia de procesos consta de cinco procesos distribuidos de la siguiente manera:

P1

$$A = C * B$$

$$P2$$

$D = A + E$

Se presume que cada proceso tiene un tiempo de ejecución t, el tiempo de ejecución total del programa de manera secuencial es igual a 5t; y el tiempo de ejecución aplicando los principios de paralelismo es de 3t.

Los procesos P1 || P5 y P5 || P2 pueden ser ejecutados en paralelo. En cambio P1 y P2 no pueden ser ejecutados en paralelo ya que "A" es la variable de salida del proceso P1 y la variable de entrada del proceso P2.

Con este ejemplo hemos demostrado que el uso de las condiciones de paralelismo antes expuestas nos sirven para incrementar el *average* de ejecución de instrucciones disminuyendo con esto el tiempo de ejecución de un programa.

### 1.2. Dependencias entre instrucciones

Al analizar los principios de paralelismo antes expuestos se observa que la ejecución en paralelo de dos o más procesos depende:

- Del grado de interdependencia de datos. Se dice que existe interdependencia de datos cuando la ejecución de un proceso depende del resultado de la ejecución de otro proceso.

- Del grado de interdependencia de control. Se dice que existe interdependencia de control cuando el orden de ejecución de un programa no puede ser determinado antes de que el mismo sea ejecutado. Un ejemplo de ello es la instrucción condicional de salto en un lenguaje de alto nivel (IF).

Del grado de interdependencia de recursos. Se dice que existe interdependencia de recursos cuando dos o más procesos requieren del mismo recurso de *hardware* al escribir los resultados de salida de cada proceso.

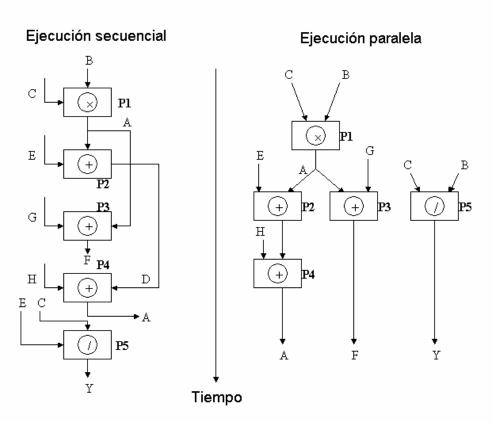

#### 1.2.1. Dependencias de datos

Las dependencias de datos pueden ser clasificadas de acuerdo con los riesgos que se presenten al tratar de trabajar las instrucciones de manera paralela con respecto al orden en el acceso de lectura o escritura generado por las instrucciones; también pueden ser clasificadas de acuerdo a la forma en que sea tratada la dependencia.

Los riesgos que existen al tratar de trabajar paralelamente las instrucciones, se pueden presentar de tres maneras diferentes:

- Leer después de escribir (RAW)

- Escribir después de leer (WAR)

- Escribir después de escribir (WAW)

De los que se pueden eliminar por medio del renombramiento de operandos, los últimos dos (WAR y WAW) generando así, las dependencias falsas, mientras que las dependencias debido a RAW, no pueden ser eliminadas, toman el nombre de dependencias verdaderas, tal como se muestra en la figura 3.

Figura 3. Clasificación de las dependencias de datos

### 1.2.1.1 Dependencias RAW (Read After Write)

Este tipo de dependencias es el más notable, ya que corresponde al grupo de dependencias verdaderas, las cuales no pueden ser eliminadas, en donde una instrucción *j* es dependiente de una instrucción *i* si cumple cualquiera de las siguientes condiciones:

La instrucción i produce un resultado que puede ser usado por la instrucción j. CONSIDERACIONDES DE DISEÑO DEL PARALELISMO INTERNO EN *HARDWARE* A NIVEL DE INSTRUCCIÓN EN MICROPROCESADORES

La instrucción j tiene una dependencia verdadera sobre la instrucción k, y

la instrucción k tiene una dependencia verdadera sobre la instrucción i.

La segunda condición, se basa en que si una instrucción es dependiente de otra sí existe una cadena de dependencias del tipo de la primera condición, entre las dos instrucciones; ésta cadena de dependencias puede ser tan larga, como el programa entero.

Para ejemplificar éste tipo de dependencia, consideremos los siguientes segmentos de código:

Dependencias de carga

load r1, a add r1, r1

$$\rightarrow$$

r2

Dependencias de registros

mul r4, r5

$$\rightarrow$$

r1 add r1, r1  $\rightarrow$  r2

Se puede observar que, en ambos ejemplos, la segunda instrucción es dependiente de la primera instrucción en sus operandos; en el primer ejemplo, el dato "a" debe ser cargado a el registro "r1" para luego ser sumado, mientras que en el segundo ejemplo la multiplicación del contenido de los registros "r4" y "r5" debe ser cargada primero a "r1", antes de ser sumada, es por ello que en la instancia de estas dependencias, dos instrucciones no se pueden ejecutar al mismo tiempo, ya que se corre el riesgo inminente de leer después de escribir.

1.2.1.2 Dependencias WAR (Write After Read)

Este tipo de dependencias se presenta cuando dos instrucciones usan el mismo registro o localización de memoria, sin haber flujo de datos o relación,

entre las instrucciones asociadas a ese registro o localización de memoria.

Una antidependencia o dependencia WAR entre una instrucción i y una instrucción j ocurre, en términos generales, cuando una instrucción j escribe a un registro o posición de memoria que la instrucción i lee, donde el orden original de las instrucciones debe ser preservado para asegurarse que i lea el valor correcto; este tipo de antidependencia forma parte del grupo de las dependencias por nombre o dependencias falsas, que al contrario de las

dependencias verdaderas, ningún valor es transmitido entre las instrucciones.

Por ejemplo, consideremos el siguiente segmento de código:

mul r2, r3  $\rightarrow$  r1

add r4, r5  $\rightarrow$  r2

Según el ejemplo, vemos que en esta dependencia existe el riesgo de escribir a r1 en la primera instrucción, después de leer el resultado de r2 de la segunda instrucción. Esta dependencia, se puede eliminar mediante renombre de registros modificando la segunda instrucción de nuestro segmento de código:

8

add r4, r5  $\rightarrow$  r7

CONSIDERACIONDES DE DISEÑO DEL PARALELISMO INTERNO EN *HARDWARE* A NIVEL DE INSTRUCCIÓN EN MICROPROCESADORES

Este renombramiento puede ser realizado estáticamente por un compilador o

dinámicamente, mediante técnicas de *hardware*.

1.2.1.3 Dependencias WAW (Write After Write)

Al igual que las dependencias del inciso anterior, este tipo de dependencias

ocurre cuando dos instrucciones usan el mismo registro o localización de

memoria, sin haber flujo de datos o relación, entre las instrucciones asociadas a

ese registro o localización de memoria, con la diferencia de que las

dependencias WAW o de salida, ocurren entre una instrucción i y una

instrucción *j* cuando escriben a el mismo registro o posición de memoria, el

orden entre las instrucciones debe ser preservado para asegurar que el valor

finalmente escrito corresponda a la instrucción j.

Si se consideran las siguientes instrucciones:

mul r1, r3  $\rightarrow$  r2

add r4, r5  $\rightarrow$  r2

Estas instrucciones pueden ser ejecutadas simultáneamente o ser

reordenadas si el registro o posición de memoria de salida es cambiado, en

9

este caso cambiando r2 de la segunda instrucción por r7:

add r4, r5  $\rightarrow$  r7

Debido a que la dependencia puede ser eliminada mediante el renombramiento de un registro o posición de memoria, sin que exista relación entre las dos instrucciones; este tipo de dependencia, pasa a ser una dependencia falsa.

### 1.2.2. Dependencias de control

Una dependencia de control, determina el ordenamiento de una instrucción *i*, respecto a una instrucción de ramificación; tanto que la instrucción *i* sea ejecutada en el orden correcto del programa y solamente cuando se deba hacer. Uno de los ejemplos más simples de dependencia de control es la dependencia de la declaración *then* como parte de la declaración *if* en una ramificación. Por ejemplo, en el segmento de código:

S1 tiene dependencia de control de p1, y S2 tiene dependencia de control de p2 pero no de p1. En general, hay dos restricciones impuestas por dependencias de control:

- Una instrucción que depende del control sobre una ramificación no se puede mover antes de la rama, para que su ejecución no se controle a lo largo de esta. Por ejemplo, no podemos tomar una instrucción desde la porción del programa correspondiente al then de una declaración if y mover esta antes de dicha declaración.

- 2. Una instrucción que no depende del control sobre una ramificación no se puede mover después de la rama, para que su ejecución se controle junto con esta. Por ejemplo, no podemos tomar una instrucción antes del declaración if y moverla dentro de la porción del then del programa.

Preservando las dependencias de control es una manera de mantener el programa en orden y que se efectúe correctamente, sin embargo, los microprocesadores actuales no trabajan de una manera conservativa, respecto a las dos restricciones anteriores, sino que se basan mediante técnicas de especulación y predicción, para anticipar, para poder trabajar lo más paralelamente posible los diferentes procesos involucrados; e este motivo de estudio en los capítulos posteriores.

#### 1.2.3. Dependencias de recursos

Este tipo de dependencias ocurre cuando dos instrucciones utilizan el mismo recurso, debido a limitaciones en *hardware* con respecto al número de unidades disponibles para realizar un proceso determinado.

Consideremos el siguiente fragmento de código:

div r1, r2  $\rightarrow$  r3

div r4, r2  $\rightarrow$  r5

La dependencia radica en la cantidad divisores insuficientes para emitir ambas instrucciones en paralelo, asumiendo que sólo existiera una unidad divisora. Entre otros posibles recursos en disputa se pueden mencionar a los buses, unidades de ejecución, búfers (almacenamiento temporal), en fin, todo aquel recurso donde por alguna circunstancia de nuestro código, resulte insuficiente para realizar instrucciones en paralelo.

### 1.3. Introducción al Pipeline de instrucciones.

Pipelining es una técnica donde múltiples instrucciones son realizadas al mismo tiempo, tiene como ventaja, el paralelismo existente entre las acciones necesarias para ejecutar una instrucción, logrando así un menor tiempo de ejecución.

Un *Pipeline* es como una línea de ensamblaje. En una línea de ensamblaje de automóviles, existen muchos pasos, donde cada uno contribuye para la construcción total del automóvil, cada paso opera en paralelo con otros pasos de un automóvil diferente. Ahora bien, en el *pipeline* de una computadora, cada paso del *pipeline* completa una parte de una instrucción y así como en la línea de ensamblaje, diferentes pasos completan diferentes partes de diferentes instrucciones en paralelo, cada uno de estos pasos es llamado *pipe stage* ó *pipe segment*.

Cada estado o segmento, recibe sus entradas de la etapa anterior y proporciona las entradas de la etapa siguiente, tal como es mostrado en la figura 4.

Figura 4. Organización de los estados del Pipeline en función del tiempo

En una línea de ensamblaje de autos, el rendimiento específico es definido por el número de autos por hora y es determinado por la rapidez con que sale un auto completo de la línea de ensamblaje; asimismo, el rendimiento de una instrucción *pipeline* se determina por la rapidez con que una instrucción completa sale del *pipeline*.

En el *pipeline* todos los estados actúan al mismo tiempo, donde el largo de un ciclo del procesador es determinado por el tiempo requerido por el estado más lento, este es usualmente un ciclo de reloj; aunque algunas veces son utilizados dos ciclos de reloj y muy rara vez una cantidad mayor de ciclos.

Uno de los objetivos principales del diseñador de microprocesadores es balancear el tiempo de ejecución de cada estado del *pipeline*; al lograr este, el tiempo por instrucción en un procesador *pipeline* asumiendo condiciones ideales es igual a:

Tiempo por instrucción sobre un procesador sin *pipeline*Número de estados del *pipeline*

Sobre estas condiciones, el aumento de productividad es proporcional al número de estados (*pipe stages*), tal como una línea de ensamblaje de automóviles con *n* estados, que puede producir automóviles tan rápido como *n* veces. Usualmente, los estados no están perfectamente balanceados, además de ello, pipelining posee otras desventajas.

La técnica de *pipeline* reduce el tiempo promedio de ejecución por instrucción, dependiendo la base; la reducción puede ser vista como una disminución del número de ciclos de reloj por instrucción (*CPI*), como decremento en el tiempo del ciclo de reloj o como una combinación. Si tomamos el primer punto de vista de que un procesador toma múltiples ciclos de reloj por instrucción, el *pipeline* es visto como una reducción del CPI; este éste el punto primordial que debe tomarse.

En el segundo punto de vista un procesador toma un largo ciclo de reloj por instrucción, entonces el *pipeline* disminuye el tiempo del ciclo de reloj. Aquí el *pipeline* es una técnica implementada que explota el paralelismo en un flujo secuencial de instrucciones.

### Las características del pipeline son:

- Subdivisión de la ejecución en fases (segmentos ó estados).

- Cada fase se asigna a una etapa hardware diferente.

- Fases de igual duración (balanceadas).

- Una etapa recibe sus entradas de la etapa anterior y proporciona las entradas, de la etapa siguiente.

- Etapas sincronizadas con la señal de reloj.

- Duración de una fase: un ciclo de reloj, algunas veces dos y rara vez más.

En la subdivisión de la ejecución por fases (*pipe segments*) al trabajar con varias instrucciones, se tiene la ventaja del paralelismo existente entre las acciones necesarias para ejecutar una instrucción, que cada fase ejecuta una acción diferente, así se pueden trabajar diferentes fases de distintas instrucciones paralelamente, tal como se muestra en la figura 5.

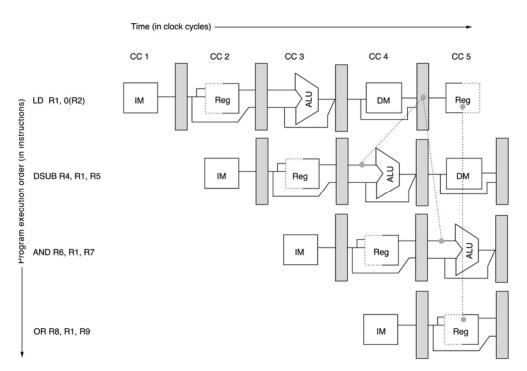

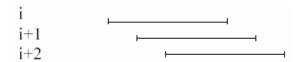

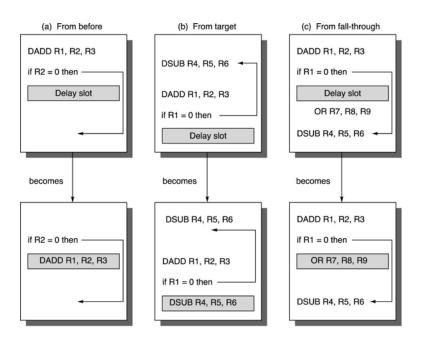

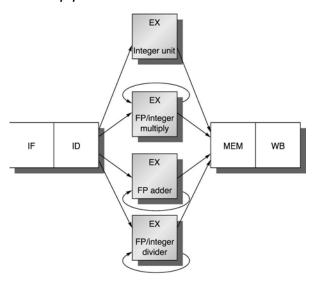

Figura 5. Segmentación de instrucciones y su ejecución.

Según el ejemplo de la figura 5, vemos que la ejecución de instrucciones ha sido segmentada en cuatro diferentes fases numeradas de 1 a 4, donde se puede observar respecto a la línea de tiempo, que al ejecutarse el primer segmento de la instrucción 4, justamente en el mismo tiempo se ejecutan los segmentos 4, 3 y 2 de las tres instrucciones anteriores, por orden de aparición, respectivamente, así se logra la ejecución de cuatro instrucciones en paralelo, justamente desde ese momento en adelante, esto se logra únicamente en un caso ideal.

Los problemas para lograr una ejecución ideal y un aprovechamiento máximo del tiempo utilizando la técnica de *pipeline* radican en la existencia de dependencias y sus riesgos entre instrucciones, así como en el uso efectivo de cada segmento de los diferentes tipos de instrucciones.

### 1.4. Paralelismo en software y paralelismo en hardware

Paralelismo en software es la capacidad de ejecutar un programa paralelamente sin tomar en cuenta el hardware con que va ser ejecutado. El paralelismo en *software* es considerado como el caso ideal de la ejecución de los procesos, ya que no toma en cuenta las limitantes del *hardware* con que el mismo va ser ejecutado; mientras que paralelismo en *hardware* es la capacidad de ejecutar un programa paralelamente tomando en consideración el *hardware* con que va a ser ejecutado.

Un ejemplo claro se observa, en el modo de ejecución del siguiente comentario de programa:

| Mov Ax, [A] | $Ax \leftarrow Mem[A]$       |

|-------------|------------------------------|

| Mov Bx, [B] | $Bx \leftarrow Mem[B]$       |

| Mul Ax, Bx  | $Ax \leftarrow Ax \times Bx$ |

| Mov Cx, [C] | $Cx \leftarrow Mem[C]$       |

| Mov Dx, [D] | $Dx \leftarrow Mem[D]$       |

| Mul Cx, Dx  | $Cx \leftarrow Cx \times Dx$ |

| Add Ax, Cx  | Ax←Ax + Cx                   |

El programa presentado está compuesto por siete instrucciones (cuatro instrucciones de movimiento de una posición de memoria a un registro, dos instrucciones de multiplicación de registros y una instrucción de suma de registros). El gráfico de interdependencia de este grupo de instrucciones se puede observar en la figura 6.

Paralelismo en Hardware Paralelismo en Software M1Ciclo 1 (M1) Ciclo 1 Ciclo 2 Ciclo 3 Ciclo 2 Ciclo 4 Ciclo 3 Ciclo 5 AXProcesador con capacidad de ejecutar Paralelismo sin un acceso a la memoria y una limitaciones de operación aritmética simultáneamente hardware.

Figura 6. Paralelismo en hardware y paralelismo en software

El diagrama de paralelismo en software representa el caso ideal con que dicho programa puede ser ejecutado; la ejecución de las siete instrucciones se realiza solamente en tres ciclos de máquina. Por otro lado, las limitantes que genera la ejecución de este mismo programa con un *hardware* en particular (procesador con capacidad de ejecutar un acceso a la memoria y una operación aritmética simultáneamente) obteniendo cinco ciclos de máquina para ejecutar el programa.

Tomando como base el ejemplo anterior, la ejecución paralela de un programa se mide mediante el parámetro conocido como Promedio de Ejecución Paralela (PEP). Este parámetro se define como la relación entre el número de procesos del programa y el número de ciclos de máquina realizados en su ejecución. Su expresión matemática es:

Por consiguiente, el promedio de ejecución paralela en *software* para este ejemplo es: 7/3 = 2.33 y el promedio de ejecución paralela en *hardware* es: 7/5 = 1.4, donde es notable observar que el promedio de ejecución paralela en *software* es aproximadamente un 67% mayor que el PEP en *hardware*.

En el paralelismo en *hardware* y en *software* es importante hacer notar que ambos están sujetos a las dependencias y riesgos en la ejecución paralela de instrucciones, mencionadas con anterioridad, donde el concepto de paralelismo en *software*, no toma en cuenta las dependencias de recursos, limitantes físicas y arquitectura de nuestro procesador, por lo que posee como única limitante las dependencias de datos y de control entre instrucciones, no pudiendo ser eliminadas las dependencias *RAW*.

### 1.5. Conceptos de planificación de instrucciones

El concepto de planificación nace de acuerdo con la forma como se ejecute la detección y resolución de dependencias entre instrucciones, como mejora en el rendimiento de los microprocesadores.

El enfoque de la planificación en un microprocesador, se puede desarrollar, ya sea, por medio de herramientas de *hardware* o *software* (compiladores) o una combinación de ambas; toma los nombres de planificación dinámica ó planificación estática, respectivamente; lo anterior se muestra en la siguiente tabla.

Tabla I. Tipos de planificación

| Tipo de Planificación      | Planificación | ¿Cómo recibe le código      |

|----------------------------|---------------|-----------------------------|

|                            | Realizada por | el procesador?              |

|                            |               | Libre de dependencias       |

| Estática (Reforzada por la | Compilador    | conflictivas y optimizado   |

| optimización del código).  |               | para su ejecución paralela. |

| Dinámica (pura)            | Procesador    | No optimizado y con         |

|                            |               | dependencias                |

| Dinámica (reforzada por el | Procesador y  | Optimizado para ejecución   |

| compilador)                | Compilador    | paralela pero con           |

|                            |               | dependencias                |

|                            |               |                             |

El enfoque de planificación dinámica (hardware-intensive) es dominante en el mercado de servidores y computadoras personales y es utilizado en una amplio rango de procesadores, incluyendo el Pentium III y 4; el Athlon; el MIPS R10000/12000; el Sun UltraSPARC III; el Power PC 603, G3 y G4; y el Alpha 21264, entre otros. Mientras que el enfoque estático (compiler-intensive), ha visto mayor adopción en el mercado de microprocesadores de aplicación especifica (embedded processors), una de las excepciones es la arquitectura IA-64 con el procesador Itanium desarrollado por Intel, tal como se muestra en la siguiente tabla.

Tabla II. Características principales de las diferentes arquitecturas de microprocesadores y algunos ejemplos

| Arquitectura Enfoque de |                                 | Detección de    | Planificación   | Ejecución         |                    |

|-------------------------|---------------------------------|-----------------|-----------------|-------------------|--------------------|

|                         | estructura                      | dependencias    |                 | de instrucciones  | Ejemplos           |

| Superescalar            |                                 |                 |                 |                   | Sun UltraSparc II/ |

| (estático)              | dinámico                        | hardware        | Estática        | en orden          |                    |

| Superescalar            |                                 |                 |                 | Algunas fuera de  |                    |

| (dinámico)              | dinámico                        | hardware        | Dinámica        | orden             | IBM Power 2        |

|                         |                                 |                 |                 |                   | Pentium III/IV     |

| Superescalar            | dinámico                        | hardware        | dinámica con    | Fuera de orden    | MIPS R10K, Alpha   |

| (especulativo)          |                                 |                 | especulación    | con especulación  | 21264, HP PA 850   |

| (copedulative)          |                                 |                 |                 |                   | IBM RS64III        |

|                         |                                 |                 |                 | Sin riesgos entre |                    |

| VLIW/LIW                | estático                        | software        | Estática        | paquetes          | Trimedia, i860     |

|                         | VEIWEIW Columb Solvato Estation |                 | emitidos        |                   |                    |

| EPIC                    | Muy estático                    | Muy orientada a |                 | Dependencias      |                    |

|                         | software                        | Muy estática    | marcadas por el | Itanium I y II    |                    |

| ay oo                   | .nay colation                   | compilador      |                 |                   |                    |

### 1.5.1. Planificación dinámica

La mayoría de los procesadores actuales son procesadores segmentados con una organización superescalar. Un procesador segmentado es aquel que divide la ejecución de una instrucción en diversas etapas, de forma que tan pronto como una instrucción finaliza una etapa n, a la vez que està realizando la etapa n+1, la siguiente instrucción puede llevar a cabo la etapa n, así se usa la técnica de *pipeline*, consiguiendo ejecutar varias instrucciones a la vez.

Un procesador superescalar es capaz de procesar más de una instrucción simultáneamente en cada una de las etapas (el símil sería tener varias cadenas de montaje ó varios *pipelines*), de esta manera se aumenta el paralelismo a nivel de instrucción. La mayoría de los procesadores superescalares actuales disponen de un mecanismo de planificación dinámica de instrucciones. Es decir, las instrucciones no se ejecutan en el orden en que aparecen en el programa sino que el *hardware* decide en que orden se ejecutan para un mayor rendimiento. Por eso, a estas máquinas también se les denomina procesadores con *ejecución fuera de orden*. La siguiente figura, muestra una organización típica de un procesador superescalar.

Figura 7. Organización típica de un procesador superescalar

Fuente: González, Antonio. Tendencias en la microarquitectura de los procesadores. Pág. 3.

El procesador dispone de una memoria cache de instrucciones, donde en cada ciclo, la unidad de búsqueda va a traer varias instrucciones. A continuación las instrucciones son decodificadas y a la vez los operandos registro son renombrados. El renombramiento de registros tiene por objetivo que los operandos destino de todas las instrucciones cuya ejecución ha empezado, pero no finalizado tengan un identificador diferente. De esta forma se eliminan las llamadas dependencias de nombre (WAR y WAW). Al reducir el número de dependencias, aumenta la cantidad de paralelismo que se puede explotar.

Tras la etapa de decodificación las instrucciones son despachadas (dispatched) a la cola de instrucciones y al buffer de reordenación. Las instrucciones permanecen en la cola de instrucciones hasta que pueden iniciar su ejecución, mientras que en el buffer de reordenación están hasta que el procesador está seguro de que su ejecución es correcta y no debe deshacerse. Los procesadores actuales realizan muchas actividades de forma especulativa, es decir, sin estar completamente seguros de si son correctas. Esto se hace para adelantar dichas actividades pero, en caso de fallo de especulación, éstas deben deshacerse.

La cola de instrucciones es inspeccionada en cada ciclo por un *hardware* que se encarga de determinar que instrucciones pueden iniciar la ejecución, o *emitirse*. Para ello, una instrucción debe de tener todos sus operandos, y los recursos que necesita deben de estar libres.

Tras emitirse las instrucciones son ejecutadas y al finalizar escriben el resultado. Tras ello la instrucción es retenida en el procesador hasta que se está seguro de que su ejecución no debe deshacerse. Para ello, las instrucciones abandonan el procesador (se *gradúan*) en orden secuencial.

De lo anterior, se puede observar, que una planificación dinámica explota el nivel de paralelismo, mediante el enfrentamiento al problema de las dependencias, tal como se muestra en la siguiente tabla:

Tabla III. Estrategias de emisión de instrucciones utilizadas en la planificación dinámica

| Qué hacer con:                    | Solución alternativa, planificando          |  |  |  |  |  |

|-----------------------------------|---------------------------------------------|--|--|--|--|--|

|                                   | dinámicamente                               |  |  |  |  |  |

| Dependencias falsas (WAR,WAW)     | Evitar Detenciones: Renombre de registros.  |  |  |  |  |  |

| en registros.                     |                                             |  |  |  |  |  |

| Dependencias de control           | Especulación en saltos (no esperar por la   |  |  |  |  |  |

|                                   | resolución del salto).                      |  |  |  |  |  |

| Bloqueos en la emisión            | Emisión de estaciones de reserva. Si se     |  |  |  |  |  |

| (debido a dependencias de datos). | produce un bloqueo las instrucciones        |  |  |  |  |  |

|                                   | independientes pueden emitirse aunque halla |  |  |  |  |  |

|                                   | alguna instrucción anterior bloqueada       |  |  |  |  |  |

|                                   | (ejecución fuera de orden).                 |  |  |  |  |  |

|                                   |                                             |  |  |  |  |  |

### 1.5.2. Planificación estática

La principal característica de estas arquitecturas es que el lenguaje máquina incorpora mecanismos para que el compilador pase información al *hardware* sobre determinadas características del programa. Por ejemplo, el compilador puede identificar que instrucciones son independientes. De esta manera el hardware puede ser mucho más sencillo, lo que mejora sustancialmente los problemas de tiempo de verificación y consumo de energía.

Figura 8. El proceso de compilación

El proceso de compilación general, de cualquier programa realizado en un lenguaje de alto nivel, para generar su código ensamblador respectivo, debe estar constituido de por lo menos tres pasos (tal como se muestra en la figura 8):

Análisis sintáctico y semántico del código en alto nivel: en donde se lleva a cabo la descomposición en instrucciones y expresiones, revisión de errores, generación de tabla con los nombres de los objetos y símbolos.

- 2. **Optimizaciones independientes de la máquina:** donde se realiza la simplificación de expresiones aritméticas.

- 3. **Optimizaciones a nivel-instrucción:** donde se genera el código ensamblador final.

En el último paso de compilación, involucra la planificación estática de instrucciones, que en contraste con la planificación dinámica, el compilador tiene la completa responsabilidad de crear un paquete de instrucciones que puede ser simultáneamente emitido, donde el *hardware* no realiza ninguna decisión acerca de la emisión múltiple de las instrucciones del paquete.

En la planificación estática son utilizadas diferentes técnicas de compilación, donde se reorganiza el código generado para que las instrucciones independientes se ejecuten cuanto antes y se de una optimización de la utilización del *hardware*, proporcionando así un código paralelo optimizado, en base a dependencias falsas, de control y de recursos.

A pesar de que el compilador es el encargado de realizar varias tareas, es necesario implementar algunas de las técnicas de hardware como lo es el uso indiscutible del *pipeline*, el cual recibe un código optimizado, así se aprovecha al máximo. Además, en técnicas propias de la planificación estática como lo es, la predicción estática de ramificaciones con el objetivo de eliminar las dependencias de control, puede ser también apoyada por predictores dinámicos a base de hardware, así como también lo es el uso de técnicas de especulación, todo ello con el objeto de optimizar y explotar en mayor manera el ILP.

CONSIDERACIONDES DE DISEÑO DEL PARALELISMO INTERNO EN HARDWARE A NIVEL DE INSTRUCCIÓN EN MICROPROCESADORES

# 2. CONSIDERACIONES DE DISEÑO E IMPLEMENTACIÓN DEL PIPELINE

Es importante tomar en consideración que todo diseño posee sus ventajas y distintas cualidades, que permiten adoptar un criterio adecuado en el momento de implementarlo o plantear una solución al problema que se presente.

La técnica de *pipeline*, ha sido desarrollada en diferentes versiones, sin embargo es utilizada en cualquier procesador, donde el número de unidades funcionales segmentadas, definen el número de etapas, dependiendo del tipo de instrucción.

### 2.1. Etapas y registros del pipeline.

En el capítulo uno se mostró la similitud existente entre la técnica de pipeline y una línea de montaje; estas tienen en común diferentes etapas, donde el traslape y la interdependencia entre varias de ellas, permite la ejecución paralela de etapas de diferentes instrucciones. Cada etapa realiza un tratamiento diferente, que es necesario, para la ejecución de nuestra instrucción.

Los procesadores previos al 8086 de Intel estaban limitados en su desempeño por la necesidad de realizar los dos pasos principales de ejecución del procesador: Fetch/Execute, en forma secuencial; es decir, no se puede ejecutar una instrucción hasta que se traiga de memoria (Fetch); y no podían traerse instrucciones de memoria mientras ejecutaba una instrucción, pues el procesador estaba ocupado. Por lo que un alto porcentaje del tiempo, el procesador estaba haciendo Fetch, cuando su función debiera ser ejecutar las instrucciones. La capacidad de ejecutar instrucciones sólo se ocupaba en un bajo porcentaje.

Para solucionar esto, fue implementada la arquitectura *pipeline Fetch/Execute*, en la que simplemente se divide la tarea en dos secciones: una encargada del *Fetch* (BIU), y otra del *Execute* (EU). De esta manera, existen circuitos separados para cada función, los cuales trabajan en paralelo. Si bien el proceso aún es secuencial, solamente al principio donde se requiere desperdiciar tiempo en el *Fetch*. A partir de ahí, *Fetch* va adelante del *Execute*, y trae instrucciones al procesador mientras este ejecuta las anteriores, constituyendo así un pipeline de 2 etapas.

Con el paso del tiempo, se ha ido implementando la técnica de *pipeline* de diferentes maneras, como lo vemos en el microprocesador Pentium IV con su tecnología de *hyperpipeline*, la cual está constituida de 22 a 24 etapas, mientras que en un Pentium con arquitectura P6 (Pentium Pro, Pentium II, Pentium III y Celeron), el número de etapas es acerca de 10 a 14. Por lo que dicha técnica ha obtenido un significado y aplicación global en el marco de los microprocesadores en donde los conceptos y criterios desarrollados a un microprocesador, son significativamente similares y aplicables a otros procesadores.

Un *pipeline* básico, está conformado de cinco etapas, donde cada instrucción puede ser implementada en al menos cinco ciclos de reloj, por lo que dependiendo del tipo de instrucción, puede ser tratada en etapas diferentes:

- Instruction fetch cycle (IF): en este primer ciclo, la tarea de ésta etapa es traer la instrucción de memoria de acuerdo al contador de programa (PC).

- 2. *Instruction decode/register fetch cycle* (ID): en esta etapa, se decodifica la instrucción, se preparan los registros según el código fuente y se verifican registros, si hubiese una posible ramificación.

- 3. Execution/effective address cycle (EX): en este ciclo, la ALU opera sobre los operandos preparados en el ciclo anterior, ejecutando una de tres funciones, dependediendo del tipo de instrucción:

- Referencia de Memoria: La ALU suma el registro base y el offset para formar una dirección efectiva.

- Instrucción de ALU de Registro a Registro: La ALU ejecuta la operación especificada por el código sobre los valores leídos del registro fuente.

- Instrucción de ALU de registro inmediato.

- 4. Memory access (MEM): si la instrucción es una carga, la memoria hace una lectura usando la dirección efectiva calculada en el ciclo anterior. Si la instrucción es un almacenamiento en memoria, se escriben los datos desde el registro a memoria, usando la dirección efectiva.

5. Write-back cylcle (WB): esta etapa es utilizada ya sea en una instrucción de ALU de registro a registro o en una instrucción de carga. Escribe el resultado dentro del registro si éste viene de la memoria del sistema (para una instrucción de carga) ó desde la ALU (para una instrucción de ALU).

Cada uno de los ciclos corresponde a una etapa del pipeline (*pipe stage*), como resultado de esto, el patrón de ejecución se puede trazar como en la siguiente tabla:

Tabla IV. Pipeline básico

| -                     | Número de ciclos de reloj |    |    |     |     |     |     |     |    |

|-----------------------|---------------------------|----|----|-----|-----|-----|-----|-----|----|

| Número de instrucción | 1                         | 2  | 3  | 4   | 5   | 6   | 7   | 8   | 9  |

| Instrucción I         | IF                        | ID | EX | MEM | WB  |     |     |     |    |

| Instrucción i+1       |                           | IF | ID | EX  | MEM | WB  |     |     |    |

| Instrucción i+2       |                           |    | IF | ID  | EX  | MEM | WB  |     |    |

| Instrucción i+3       |                           |    |    | IF  | ID  | EX  | MEM | WB  |    |

| Instrucción i+4       |                           |    |    |     | IF  | ID  | EX  | MEM | WB |

IF = instruction Fetch ID= instruction decode EX= execution MEM= Memory Access WB= write back

Cada instrucción toma cinco ciclos de reloj para ser completada, durante cada ciclo de reloj el *hardware* inicializará una nueva instrucción y será ejecutada alguna etapa de cinco instrucciones diferentes.

Para conocer las consideraciones que se deben de tomar en la implementación, se debe determinar que sucede en cada uno de los ciclos del procesador.

Por ejemplo, debemos estar seguros que dos diferentes operaciones no utilicen los mismos recursos en el mismo ciclo de reloj, tal es el caso de que si poseemos en nuestro procesador una sola ALU no podremos calcular al mismo tiempo una operación de suma con el cálculo de una dirección efectiva. De esta manera debemos garantizar que el traslape de instrucciones en el *pipeline* no cause cierto conflicto.