INTRODUCCIÓN DEL LENGUAJE ENSAMBLADOR PARA LA ARQUITECTURA

ARM UTILIZANDO EL ENTORNO DE DESARROLLO KEIL UVISION4, BAJO EL MODELO

CONSTRUCTIVISTA DE EDUCACIÓN, COMO VIRTUALIZACIÓN DE LOS TEMAS

IMPARTIDOS EN EL CURSO DE ELECTRÓNICA 5 EN LA ESCUELA DE INGENIERÍA

MECÁNICA ELÉCTRICA, FACULTAD DE INGENIERÍA, UNIVERSIDAD DE SAN CARLOS

DE GUATEMALA

## Miguel Bernabé Tavico Laynez

Asesorado por la Inga. Ingrid Rodríguez de Loukota

Guatemala, octubre de 2021

#### UNIVERSIDAD DE SAN CARLOS DE GUATEMALA

### FACULTAD DE INGENIERÍA

INTRODUCCIÓN DEL LENGUAJE ENSAMBLADOR PARA LA ARQUITECTURA ARM

UTILIZANDO EL ENTORNO DE DESARROLLO KEIL UVISION4, BAJO EL MODELO

CONSTRUCTIVISTA DE EDUCACIÓN, COMO VIRTUALIZACIÓN DE LOS TEMAS

IMPARTIDOS EN EL CURSO DE ELECTRÓNICA 5 EN LA ESCUELA DE INGENIERÍA

MECÁNICA ELÉCTRICA, FACULTAD DE INGENIERÍA, UNIVERSIDAD DE SAN CARLOS

DE GUATEMALA

TRABAJO DE GRADUACIÓN

PRESENTADO A LA JUNTA DIRECTIVA DE LA FACULTAD DE INGENIERÍA POR

#### MIGUEL BERNABÉ TAVICO LAYNEZ

ASESORADO POR LA INGA. INGRID SALOMÉ RODRÍGUEZ DE LOUKOTA

AL CONFERÍRSELE EL TÍTULO DE

**INGENIERO ELECTRÓNICO**

GUATEMALA, OCTUBRE DE 2021

## UNIVERSIDAD DE SAN CARLOS DE GUATEMALA FACULTAD DE INGENIERÍA

### NÓMINA DE JUNTA DIRECTIVA

| DECANA  | Inga. Aurelia Anabela Cordova Estrada |

|---------|---------------------------------------|

| VOCAL I | Ing. José Francisco Gómez Rivera      |

VOCAL II Ing. Mario Renato Escobedo Martínez

VOCAL III Ing. José Milton de León Bran

VOCAL IV Br. Kevin Vladimir Armando Cruz Lorente

VOCAL V Br. Fernando José Paz González SECRETARIO Ing. Hugo Humberto Rivera Pérez

## TRIBUNAL QUE PRACTICÓ EL EXAMEN GENERAL PRIVADO

DECANO Ing. Pedro Antonio Aguilar Polanco

EXAMINADOR Ing. Carlos Eduardo Guzmán Salazar

EXAMINADOR Ing. Byron Odilio Arrivillaga Méndez

EXAMINADOR Ing. Armando Alonso Rivera Carrillo

SECRETARIA Inga. Lesbia Magalí Herrera López

#### HONORABLE TRIBUNAL EXAMINADOR

En cumplimiento con los preceptos que establece la ley de la Universidad de San Carlos de Guatemala, presento a su consideración mi trabajo de graduación titulado:

INTRODUCCIÓN DEL LENGUAJE ENSAMBLADOR PARA LA ARQUITECTURA ARM

UTILIZANDO EL ENTORNO DE DESARROLLO KEIL UVISION4, BAJO EL MODELO

CONSTRUCTIVISTA DE EDUCACIÓN, COMO VIRTUALIZACIÓN DE LOS TEMAS

IMPARTIDOS EN EL CURSO DE ELECTRÓNICA 5 EN LA ESCUELA DE INGENIERÍA

MECÁNICA ELÉCTRICA, FACULTAD DE INGENIERÍA, UNIVERSIDAD DE SAN CARLOS

DE GUATEMALA

Tema que me fuera asignado por la Dirección de la Escuela de Ingeniería Mecánica Eléctrica, con fecha 03 de junio de 2019.

Miguel Bernabé Tavico Laynez

Ingeniero

Julio César Solares Peñate

Coordinador del Área de Electrónica

Escuela de Ingeniería Mecánica Eléctrica

Facultad de Ingeniería, USAC.

Apreciable Ingeniero Solares,

Me permito dar aprobación al trabajo de graduación titulado "Introducción del lenguaje ensamblador para la arquitectura ARM utilizando el entorno de desarrollo Keil uVision4, bajo el modelo constructivista de educación, como virtualización de los temas impartidos en el curso de Electrónica 5 en la Escuela de Ingeniería Mecánica Eléctrica, Facultad de Ingeniería, Universidad de San Carlos de Guatemala", del señor Miguel Bernabé Tavico Laynez, por considerar que cumple con los requisitos establecidos.

Por tanto, el autor de este trabajo de graduación y, yo, como su asesora, nos hacemos responsables por el contenido y conclusiones de este.

Sin otro particular, me es grato saludarle.

Atentamente,

Inga. Ingrid Rodríguez de Loukota Colegiada 5,356 Asesora

> Ingrid Rodríguez de Loukota Ingeniera en Electrónica colegiado 5356

#### UNIVERSIDAD DE SAN CARLOS DE GUATEMALA

Guatemala, 20 de julio de 2021

PDIRECCION ESCUELA DE INGENIERIA MECANICA ELECTRICA

Señor director Armando Alonso Rivera Carrillo Escuela de Ingeniería Mecánica Eléctrica Facultad de Ingeniería, USAC

#### Estimado Señor director:

Por este medio me permito dar aprobación al Trabajo de Graduación titulado: INTRODUCCIÓN DEL LENGUAJE ENSAMBLADOR PARA LA ARQUITECTURA ARM UTILIZANDO EL ENTORNO DE DESARROLLO KEIL UVISION4, BAJO EL MODELO CONSTRUCTIVISTA DE EDUCACIÓN, COMO VIRTUALIZACIÓN DE LOS TEMAS IMPARTIDOS EN EL CURSO DE ELECTRÓNICA 5 EN LA ESCUELA DE INGENIERÍA MECÁNICA ELÉCTRICA, FACULTAD DE INGENIERÍA, UNIVERSIDAD DE SAN CARLOS DE GUATEMALA, desarrollado por el estudiante Miguel Bernabé Tavico Laynez, ya que considero que cumple con los requisitos establecidos.

Sin otro particular, aprovecho la oportunidad para saludarlo.

Atentamente,

ID Y ENSEÑAD A TODOS

Ing. Julio César Solares Peñate Coordinador de Electrónica

#### REF. EIME 116. 2021.

El Director de la Escuela de Ingeniería Mecánica Eléctrica, después de conocer el dictamen del Asesor, con el Visto Bueno del Coordinador de Área, al trabajo de Graduación del estudiante; BERNABÉ TAVICO LAYNEZ titulado: INTRODUCCIÓN DEL LENGUAJE ENSAMBLADOR PARA LA ARQUITECTURA ARM UTILIZANDO EL ENTORNO DE DESARROLLO KEIL BAJO MODELO CONSTRUCTIVISTA uVISION4. EL DE EDUCACIÓN, COMO VIRTUALIZACIÓN DE LOS TEMAS IMPARTIDOS EN EL CURSO DE ELECTRÓNICA 5 EN LA MECÁNICA INGENIERÍA ELÉCTRICA, ESCUELA DE INGENIERÍA, UNIVERSIDAD **FACULTAD** DE DE SAN CARLOS DE GUATEMALA, procede a la autorización del mismo.

Ing. Armando Alonso Rivera Carrillo

GUATEMALA, 12 DE AGOSTO

2,021.

DIRECCION ESCUELA DE INGENIERIA

Decanato Facultad de Ingeniería 24189101 – 24189102 secretariadecanato@ingenieria.usac.edu.gt

DTG. 545-2021

DECANO FACULTAD DE INGENIERIA

La Decana de la Facultad de Ingeniería de la Universidad de San Carlos de Guatemala, luego de conocer la aprobación por parte del Director de la Escuela de Ingeniería Mecánica Eléctrica, al Trabajo de Graduación titulado: INTRODUCCIÓN DEL LENGUAJE ENSAMBLADOR PARA LA ARQUITECTURA ARM UTILIZANDO EL ENTORNO DE DESARROLLO KEIL UVISIONA, BAJO EL MODELO CONSTRUCTIVISTA DE EDUCACIÓN, COMO VIRTUALIZACIÓN DE LOS TEMAS IMPARTIDOS EN EL CURSO DE ELECTRÓNICA 5 EN LA ESCUELA DE INGENIERÍA MECÁNICA ELÉCTRICA, FACULTAD DE INGENIERÍA, UNIVERSIDAD DE SAN CARLOS DE GUATEMALA, presentado por el estudiante universitario: Miguel Bernabé Tavico Laynez, y después de haber culminado las revisiones previas bajo la responsabilidad de las instancias correspondientes, autoriza la impresión del mismo.

IMPRÍMASE:

Inga. Anabéla Cordova Estrac

Decana

Guatemala, octubre de 2021

AACE/cc

## **ACTO QUE DEDICO A:**

**Dios** Por darme la fortaleza y sabiduría durante toda

mi carrera.

Mis padres Antonia Laynez y Bernabé Tavico por ser los

pilares de mi vida.

Mis hermanas Dra. Ingrid, Dra. Marycruz y Kimberly Tavico por

su apoyo.

Mis abuelos Por sus sabios consejos, aprecio y cariño

Mi familia Especialmente a las que me apoyaron y por

decisión de la vida ya no están.

#### **AGRADECIMIENTOS A:**

Universidad de San Carlos de Guatemala Por abrirme las puertas y brindarme una educación de alta calidad.

Facultad de Ingeniería

Por brindarme todos los conocimientos necesarios para ejercer como profesional.

Mis amigos de la Facultad

Fabiola España y Manuel Fernández por su apoyo incondicional durante y al final de la carrera.

Mis amigos de la Facultad Lesther Meoño, Luis Álvarez, José Monroy, Jonathan Medina, Steve Contreras, Ricardo Ball, Elizabeth Lux, Estuardo Chirix, Kevin Ayrton, Ronald Sandoval, Kelvin Garcia, Fernando Reyes, Luis Estrada, Luis Herrera y Esvin Paredes, por su apoyo durante la carrera.

Mis amigos de la Facultad

Luis Calderón, Rafa Toj, Dennis Fuentes, Kevin Franco, Victor Tórtola, Andrés Días, Juan Silva y Betuel Flores por su apoyo al inicio y durante la carrera.

Otros

Personas que por decisión de la vida ya no están presentes y otras por decisión propia.

# Miguel Tavico

Por tener la fortaleza y perseverancia para culminar esta etapa de la vida.

# **ÍNDICE GENERAL**

| ÍNDIC | E DE ILL | JSTRACIO                                            | NES            |                                 | IX   |

|-------|----------|-----------------------------------------------------|----------------|---------------------------------|------|

| LISTA | A DE SÍM | BOLOS                                               |                |                                 | (VII |

| GLOS  | SARIO    |                                                     |                |                                 | XIX  |

| RESL  | JMEN     |                                                     |                | X                               | XIII |

| OBJE  | TIVOS    |                                                     |                | x                               | ίχV  |

|       |          |                                                     |                | XX                              |      |

|       |          |                                                     |                | ,                               |      |

| 1.    | APREN    |                                                     |                | ÓN                              |      |

|       | 1.1.     | La educa                                            | ición          |                                 | 1    |

|       |          | 1.1.1.                                              | Enseñanza y    | Aprendizaje                     | 3    |

|       |          |                                                     | 1.1.1.1. T     | eorías del aprendizaje          | 3    |

|       | 1.2.     | Precursores de las teorías modernas del aprendizaje |                |                                 | 5    |

|       |          | 1.2.1.                                              | Teoría del ap  | rendizaje                       | 5    |

|       |          | 1.2.2.                                              | Racionalismo   |                                 | 6    |

|       |          | 1.2.3.                                              | Empirismo      |                                 | 6    |

|       | 1.3.     | El cons                                             | tructivismo en | la educación como método de     |      |

|       |          | enseñan                                             | za             |                                 | 7    |

|       |          | 1.3.1.                                              | Jean Piaget    |                                 | 7    |

|       |          |                                                     | 1.3.1.1. E     | l origen del pensamiento humano | 8    |

|       |          | 1.3.2.                                              | Lev Vygotsky   |                                 | 8    |

|       |          |                                                     | 1.3.2.1. M     | létodo de enseñanza             | 9    |

|       |          | 1.3.3.                                              | David Ausube   | əl                              | . 10 |

|       |          | 1.3.4.                                              |                | onstructivismo?                 |      |

|       | 1.4.     |                                                     | _              | ı Piaget, Vygotsky y Ausubel    |      |

|       | 1.5.     | -                                                   | _              | ije constructivistas            |      |

|    | 1.6.   | La ensenanza dentro dei constructivismo12 |                                              |    |  |  |

|----|--------|-------------------------------------------|----------------------------------------------|----|--|--|

|    |        | 1.6.1.                                    | Enseñanza por el descubrimiento              | 14 |  |  |

|    |        | 1.6.2.                                    | Enseñanza por indagación                     | 14 |  |  |

|    |        | 1.6.3.                                    | Aprendizaje asistido por los pares           | 15 |  |  |

|    |        | 1.6.4.                                    | Aprendizaje cooperativo                      | 15 |  |  |

|    | 1.7.   | Evaluar el                                | aprendizaje                                  | 15 |  |  |

|    |        | 1.7.1.                                    | Observación directa                          | 16 |  |  |

|    |        | 1.7.2.                                    | Examen escrito                               | 17 |  |  |

|    |        | 1.7.3.                                    | Exámenes Orales                              | 17 |  |  |

|    |        | 1.7.4.                                    | Calificación de terceros                     | 18 |  |  |

|    |        | 1.7.5.                                    | Autoevaluaciones                             | 18 |  |  |

|    | 1.8.   | Tecnologí                                 | as de la información y la comunicación (TIC) | 19 |  |  |

|    |        | 1.8.1.                                    | E-learning                                   | 21 |  |  |

|    |        |                                           | 1.8.1.1. Comunicación Síncrona               | 22 |  |  |

|    | 1.9.   | Herramier                                 | ntas usadas con la comunicación síncrona     | 22 |  |  |

|    |        | 1.9.1.                                    | Chat                                         | 22 |  |  |

|    |        | 1.9.2.                                    | Webinars                                     | 23 |  |  |

|    |        | 1.9.3.                                    | Videollamadas                                | 23 |  |  |

|    | 1.10.  | Comunica                                  | nción Asíncrona                              | 23 |  |  |

| 2. | KEIL®  | MDK UTII                                  | LIZANDO LENGUAJE ENSAMBLADOR PARA            |    |  |  |

|    | PROCES | SADORES                                   | ARM® CORTEX®-M4                              | 25 |  |  |

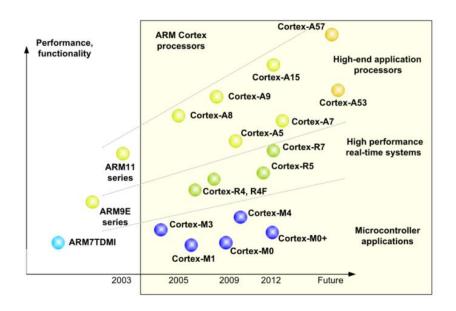

|    | 2.1.   | SoC (Syst                                 | tem on a Chip)                               | 28 |  |  |

|    | 2.2.   | Procesado                                 | or y Microprocesador                         | 29 |  |  |

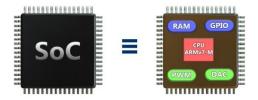

|    |        | 2.2.1.                                    | Microprocesador                              | 29 |  |  |

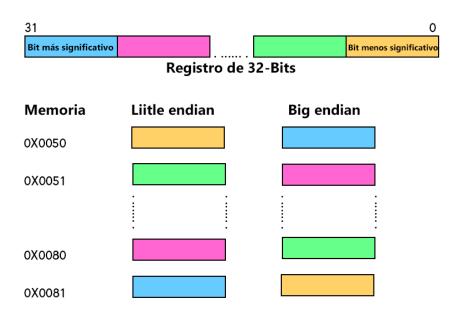

|    | 2.3.   | Endianne                                  | SS                                           | 31 |  |  |

|    |        | 2.3.1.                                    | Big-Endian                                   | 31 |  |  |

|    |        | 2.3.2.                                    | Little-Endian                                |    |  |  |

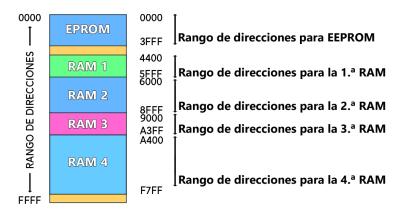

|    | 2.4.   | Rango de                                  | direcciones para Cortex-M4                   | 32 |  |  |

|    |        | _                                         |                                              |    |  |  |

| 2.5.  | Arquitect | tura de los procesadores                         | . 35 |

|-------|-----------|--------------------------------------------------|------|

|       | 2.5.1.    | RISC                                             | . 37 |

|       | 2.5.2.    | CISC                                             | . 37 |

| 2.6.  | Von Neu   | mann & Harvard                                   | . 38 |

|       | 2.6.1.    | Arquitectura Von Neumman                         | . 39 |

|       | 2.6.2.    | Arquitectura Harvard                             | . 40 |

|       | 2.6.3.    | Arquitectura Harvard modificada                  | . 40 |

| 2.7.  | La Famil  | ia Cortex                                        | . 41 |

|       | 2.7.1.    | Cortex A                                         | . 42 |

|       | 2.7.2.    | Cortex R                                         | . 42 |

|       | 2.7.3.    | Cortex M                                         | . 43 |

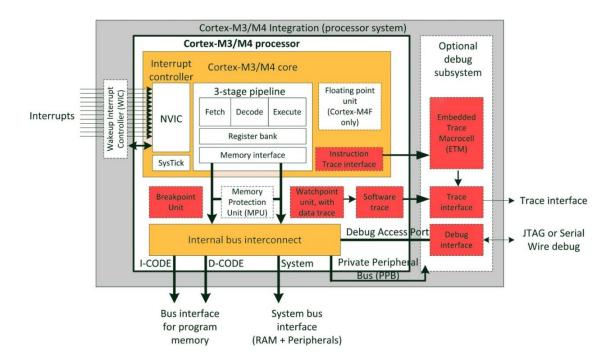

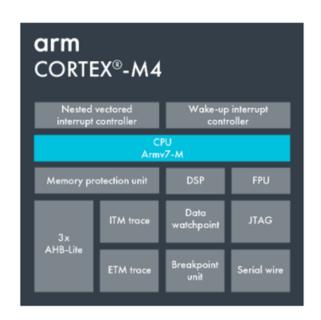

| 2.8.  | Cortex M  | 14                                               | . 45 |

|       | 2.8.1.    | Instrucciones DSP                                | . 48 |

|       | 2.8.2.    | Unidad de punto flotante                         | . 49 |

| 2.9.  | Lenguaje  | e de bajo nivel                                  | . 50 |

|       | 2.9.1.    | Bits a Comandos                                  | . 50 |

| 2.10. | Lenguaje  | e ensamblador                                    | . 52 |

|       | 2.10.1.   | Jerarquía de una computadora                     | . 52 |

| 2.11. | Arquitect | tura y lenguaje ensamblador                      | . 55 |

|       | 2.11.1.   | Sistema numérico                                 | . 55 |

| 2.12. | Sistema   | de numeración                                    | . 56 |

|       | 2.12.1.   | Sistema de numeración decimal                    | . 56 |

|       | 2.12.2.   | Sistema de numeración binario                    | . 57 |

|       | 2.12.3.   | Sistema de numeración hexadecimal                | . 58 |

| 2.13. | Software  | de desarrollo para microcontroladores basados en |      |

|       | ARM       |                                                  | . 59 |

|       | 2.13.1.   | Keil uVision®                                    | . 61 |

|       | 2.13.2.   | Componentes básicos de Keil uVision®             | . 62 |

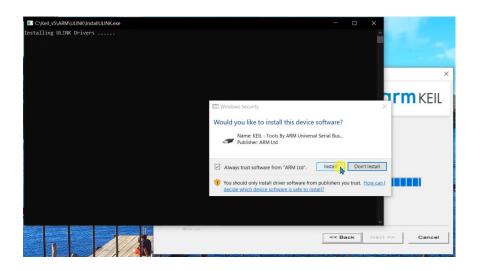

|       | 2 13 3    | Instalación del software de desarrollo Keil® MDK | 64   |

|    |         | 2.13.4.   | Instalación  | de K   | eil Uvi        | sion®4       |         |             | 65  |

|----|---------|-----------|--------------|--------|----------------|--------------|---------|-------------|-----|

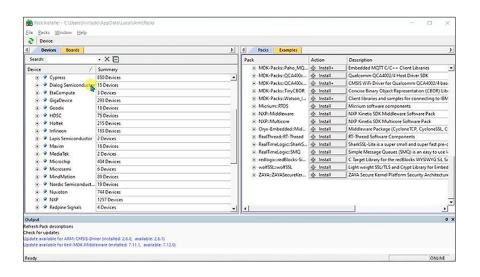

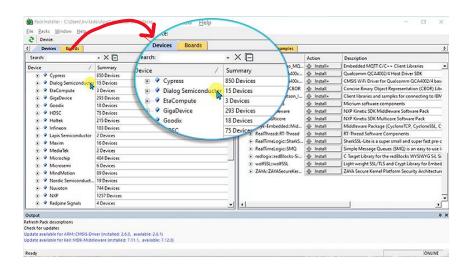

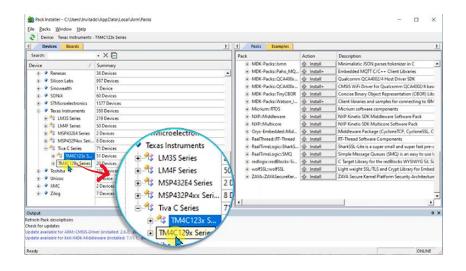

|    |         | 2.13.5.   | Instalación  | de K   | eil Uvi        | sion®5       |         |             | 70  |

|    |         | 2.13.6.   | Instalación  | de I   | os pad         | quetes p     | ara e   | el procesad | or  |

|    |         |           | Cortex®M     | TM40   | C123G          | H6PM         |         |             | 74  |

|    |         | 2.13.7.   | Instalación  | de d   | rivers .       |              |         |             | 77  |

|    |         | 2.13.8.   | Instalación  | de D   | ebug S         | Stellaris@   | () ICD  | l           | 85  |

| 3. | PROGR   | AMACIÓN   | EN LO        | S F    | PROCE          | ESADOF       | RES     | CORTEX-     | ·M  |

|    | UTILIZA | NDO ENSA  | AMBLADOR     | ₹      |                |              |         |             | 89  |

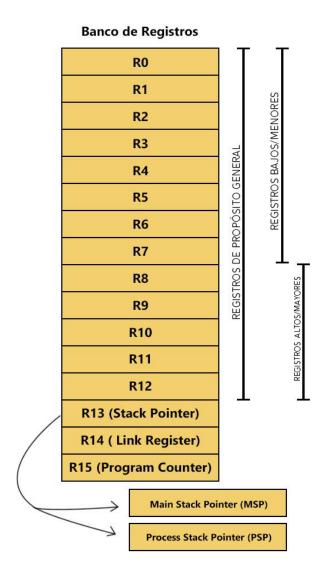

|    | 3.1.    | Registros |              |        |                |              |         |             | 89  |

|    |         | 3.1.1.    | Stack Mem    | nory   |                |              |         |             | 90  |

|    |         | 3.1.2.    | R0-R12       |        |                |              |         |             | 91  |

|    |         | 3.1.3.    | R13, Stack   | Poin   | iter (SF       | P)           |         |             | 91  |

|    |         | 3.1.4.    | R14, Link F  | Regis  | ter (LR        | 2)           |         |             | 92  |

|    |         | 3.1.5.    | R15, Progr   | am C   | counter        | (PC)         |         |             | 93  |

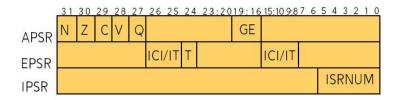

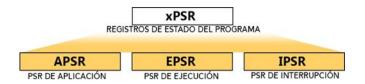

|    |         | 3.1.6.    | Registros e  | espec  | iales          |              |         |             | 93  |

|    |         | 3.1.7.    | Registro de  | e esta | ado del        | progran      | na      |             | 93  |

|    |         | 3.1.8.    | Principios b | básic  | os en e        | ensambl      | ador    |             | 96  |

|    |         |           | 3.1.8.1.     |        | axis<br>amblac | usada<br>dod |         | n lengua    | •   |

|    |         |           | 3.1.8.2.     |        |                |              |         |             |     |

|    |         |           | 3.1.8.3.     |        |                |              |         | ograma      |     |

|    |         |           | 3.1.8.4.     |        |                |              | •       |             |     |

|    |         |           | 3.1.8.5.     | Dire   | ctivas.        |              |         |             | 101 |

|    |         | 3.1.9.    | Lenguaje     | ensa   | mblado         | or unific    | ado     | o en ingle  | és  |

|    |         |           | UAL          |        |                |              |         |             | 105 |

|    |         | 3.1.10.   |              |        |                |              |         |             |     |

|    |         |           | 3 1 10 1     | Mov    | er date        | os dentro    | o del r | orocesador  | 107 |

|         | 3.1.10.2.   | Instrucciones de acceso a la             |

|---------|-------------|------------------------------------------|

|         |             | memoria110                               |

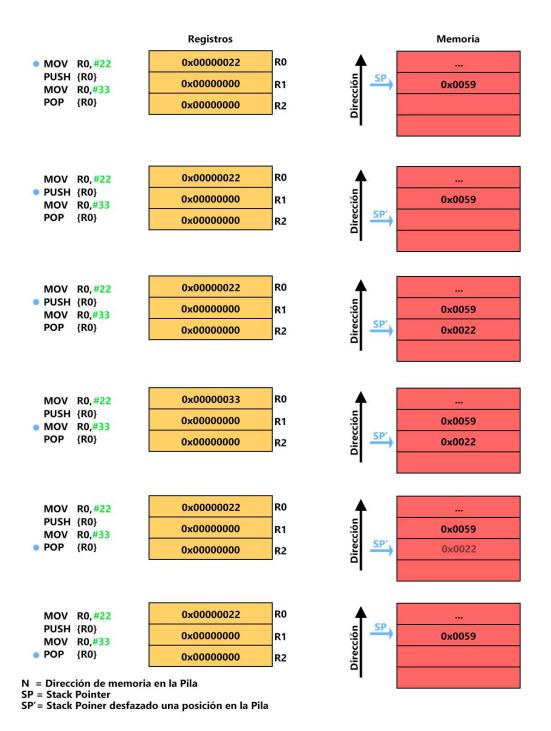

|         |             | 3.1.10.2.1. PUSH y POP 110               |

|         | 3.1.10.3.   | Operaciones Aritméticas114               |

|         | 3.1.10.4.   | Operaciones lógicas 117                  |

|         | 3.1.10.5.   | Prueba y compara 118                     |

|         | 3.1.10.6.   | Control del flujo del programa 119       |

|         |             | 3.1.10.6.1. Saltos ( <i>Branch</i> ) 120 |

|         |             | 3.1.10.6.2. Saltos (Branches)            |

|         |             | condicionados 120                        |

|         |             | 3.1.10.6.3. Llamada de función 123       |

|         |             | 3.1.10.6.4. Compara y salto              |

|         |             | condicional 123                          |

|         | 3.1.10.7.   | Otro tipo de instrucciones 125           |

|         |             | 3.1.10.7.1. NOP                          |

| 3.1.11. | Instruccion | es específicas para Cortex®-M4           |

|         | basadas e   | n DSP mejorado126                        |

|         | 3.1.11.1.   | Multiplicación e instrucciones MAC 127   |

|         | 3.1.11.2.   | Instrucciones de punto flotante 128      |

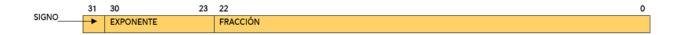

|         | 3.1.11.3.   | Números con punto flotante de            |

|         |             | precisión simple129                      |

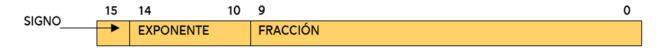

|         | 3.1.11.4.   | Números con punto flotante de            |

|         |             | precisión media130                       |

|         | 3.1.11.5.   | Números con punto flotante de doble      |

|         |             | precisión 131                            |

| 3.1.12. | Unidad de   | punto flotante en Cortex®-M4 132         |

|         | 3.1.12.1.   | Registro CPACR136                        |

|         | 3.1.12.2.   | Banco de registros para punto            |

|         |             | flotante                                 |

|    |       |         | 3.1.12.3.                                                             | FPSCR                        | 139    |  |  |  |

|----|-------|---------|-----------------------------------------------------------------------|------------------------------|--------|--|--|--|

|    |       |         | 3.1.12.4.                                                             | Opciones de la línea de coma | andos  |  |  |  |

|    |       |         |                                                                       | del compilador               | 145    |  |  |  |

| 4. | DD∩DI | EMAS DE |                                                                       | S EN LENGUAJE ENSAMBLADOF    | 0 1/17 |  |  |  |

| 4. | 4.1.  |         |                                                                       |                              |        |  |  |  |

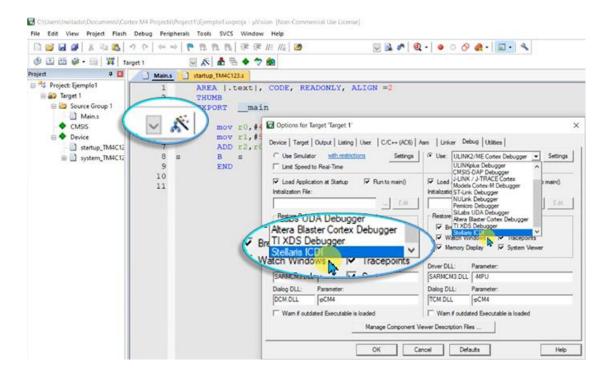

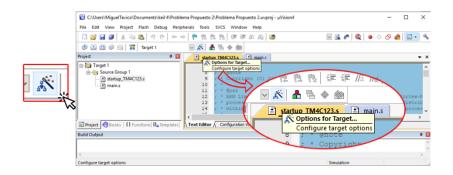

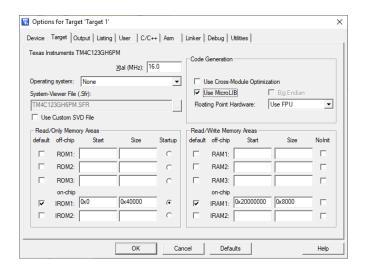

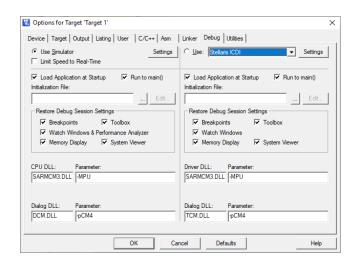

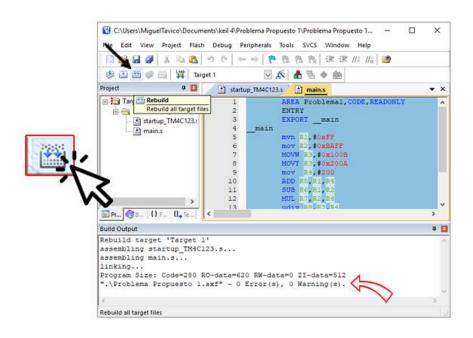

|    |       |         | Crear un proyecto nuevo en Keil® uVision14  Constructor y Depurador15 |                              |        |  |  |  |

|    | 4.2.  |         |                                                                       |                              |        |  |  |  |

|    | 4.3.  |         |                                                                       | 1                            |        |  |  |  |

|    |       | 4.3.1.  |                                                                       | el problema                  |        |  |  |  |

|    |       | 4.3.2.  |                                                                       | del problema 1               |        |  |  |  |

|    |       | 4.3.3.  |                                                                       | e la solución                |        |  |  |  |

|    | 4.4.  | Problen | na propuesto                                                          | 2                            | 158    |  |  |  |

|    |       | 4.4.1.  | Análisis d                                                            | el problema                  | 159    |  |  |  |

|    |       | 4.4.2.  | Solución o                                                            | del problema 2               | 159    |  |  |  |

|    |       | 4.4.3.  | Análisis d                                                            | e la solución                | 160    |  |  |  |

|    | 4.5.  | Problem | na propuesto                                                          | 3                            | 161    |  |  |  |

|    |       | 4.5.1.  | Análisis d                                                            | el problema                  | 161    |  |  |  |

|    |       | 4.5.2.  | Solución o                                                            | de problema 3                | 162    |  |  |  |

|    |       | 4.5.3.  | Análisis d                                                            | e la solución                | 163    |  |  |  |

|    | 4.6.  | Problem | na Propuesto                                                          | 4                            | 165    |  |  |  |

|    |       | 4.6.1.  | Análisis d                                                            | el problema                  | 165    |  |  |  |

|    |       | 4.6.2.  | Solución o                                                            | de problema 4                | 166    |  |  |  |

|    |       | 4.6.3.  | Análisis d                                                            | e la solución                | 167    |  |  |  |

|    | 4.7.  | Problem | na Propuesto                                                          | 5                            | 167    |  |  |  |

|    |       | 4.7.1.  | Análisis d                                                            | el problema                  | 168    |  |  |  |

|    |       | 4.7.2.  | Solución o                                                            | de problema 5                | 168    |  |  |  |

|    |       | 4.7.3.  | Análisis d                                                            | e la solución                | 169    |  |  |  |

|    | 4.8.  | Problem | na Propuesto                                                          | 6                            | 170    |  |  |  |

|    |       | 481     | •                                                                     | el problema                  | 170    |  |  |  |

|       | 4.8.2.  | Solución del problema 6 17  | 71         |

|-------|---------|-----------------------------|------------|

|       | 4.8.3.  | Análisis de la solución17   | 71         |

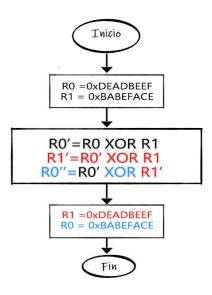

| 4.9.  | Problem | a Propuesto 717             | 73         |

|       | 4.9.1.  | Análisis del problema17     | 73         |

|       | 4.9.2.  | Solución del problema 7 17  | 74         |

|       | 4.9.3.  | Análisis de la solución17   | 75         |

| 4.10. | Problem | a Propuesto 817             | 77         |

|       | 4.10.1. | Análisis del problema17     | 77         |

|       | 4.10.2. | Solución de problema 8 17   | 79         |

|       | 4.10.3. | Análisis de la solución17   | 79         |

| 4.11. | Problem | a Propuesto 918             | 31         |

|       | 4.11.1. | Análisis del problema18     | 31         |

|       | 4.11.2. | Solución del problema 9 18  | 34         |

|       | 4.11.3. | Análisis de la solución18   | 34         |

| 4.12. | Problem | a propuesto 1018            | 36         |

|       | 4.12.1. | Análisis del problema18     | 36         |

|       | 4.12.2. | Solución del problema 10 18 | 38         |

|       | 4.12.3. | Análisis de la solución18   | 38         |

| 4.13. | Problem | a Propuesto 1118            | 39         |

|       | 4.13.1. | Análisis del problema19     | <b>)</b> ( |

|       | 4.13.2. | Solución del problema 11 19 | )1         |

|       | 4.13.3. | Análisis de la solución19   | )1         |

| 4.14. | Problem | a Propuesto 1219            | 93         |

|       | 4.14.1. | Análisis del problema19     | 93         |

|       | 4.14.2. | Solución de problema 12 19  | )4         |

|       | 4.14.3. | Análisis de solución 19     | )4         |

| 4.15. | Problem | a Propuesto 1319            | <b>)</b> 7 |

|       | 4.15.1. | Análisis del problema19     | 36         |

|       | 4 15 2  | Solución de problema 1319   | 38         |

|              | 4.15.3.  | Análisis de la Solución  | 199 |

|--------------|----------|--------------------------|-----|

| 4.16.        | Problema | Propuesto 14             | 200 |

|              | 4.16.1.  | Análisis del problema    | 201 |

|              | 4.16.2.  | Solución del problema 14 | 201 |

|              | 4.16.3.  | Análisis de la solución  | 202 |

| 4.17.        | Problema | Propuesto 15             | 204 |

|              | 4.17.1.  | Análisis del problema    | 204 |

|              | 4.17.2.  | Solución del problema 15 | 205 |

|              | 4.17.3.  | Análisis de la solución  | 205 |

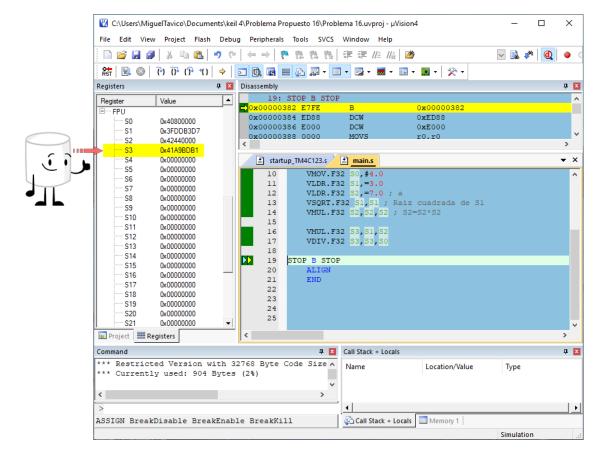

| 4.18.        | Problema | propuesto 16             | 207 |

|              | 4.18.1.  | Análisis del problema    | 207 |

|              | 4.18.2.  | Solución del problema 16 | 208 |

|              | 4.18.3.  | Análisis de la solución  | 208 |

| 4.19.        | Problema | Propuesto 17             | 210 |

|              | 4.19.1.  | Análisis del problema    | 210 |

|              | 4.19.2.  | Solución del problema 17 | 213 |

|              | 4.19.3.  | Análisis de la solución  | 214 |

| 4.20.        | Problema | Propuesto 18             | 216 |

|              | 4.20.1.  | Análisis del problema    | 216 |

|              | 4.20.2.  | Solución del problema 18 | 218 |

|              | 4.20.3.  | Análisis de la Solución  | 219 |

|              |          |                          |     |

| CONCLUSION   | ES       |                          | 221 |

| RECOMENDA    | CIONES   |                          | 223 |

| BIBLIOGRAFÍA | ١        |                          | 225 |

# **ÍNDICE DE ILUSTRACIONES**

## **FIGURAS**

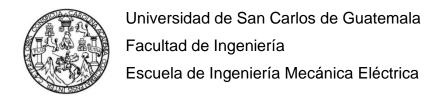

| 1.  | Versiones de procesadores ARM y sus respectivas familias | 27 |

|-----|----------------------------------------------------------|----|

| 2.  | Encapsulado de un SoC y su vista interna                 | 28 |

| 3.  | Configuración interna básica de un procesador            | 31 |

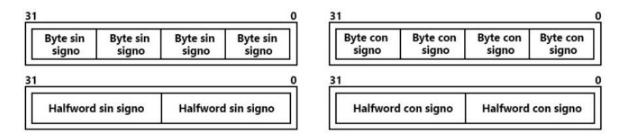

| 4.  | Almacenamiento de los bits en memoria                    | 32 |

| 5.  | Mapeado de la memoria y direcciones de un procesador     | 33 |

| 6.  | Mapa de memoria para procesador Cortex-M4                | 34 |

| 7.  | David Patterson and Carlos Séquina                       | 36 |

| 8.  | Arquitectura RISC vs CISC                                | 38 |

| 9.  | Diagrama de la arquitectura Von Neumman                  | 39 |

| 10. | Diagrama de la arquitectura Harvard                      | 40 |

| 11. | Diagrama de la arquitectura Harvard modificada           | 41 |

| 12. | Instrucciones en la familia Cortex-M                     | 44 |

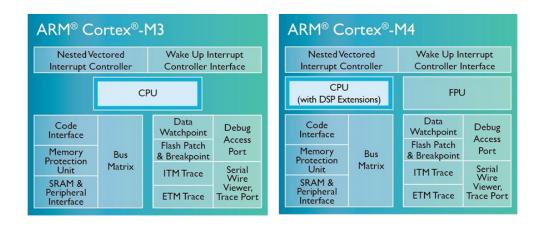

| 13. | Diagrama de bloques para Cortex®-M4 y M3                 | 46 |

| 14. | Diagrama de un Cortex-M3 y M4                            | 47 |

| 15. | Instrucción SIMD                                         | 49 |

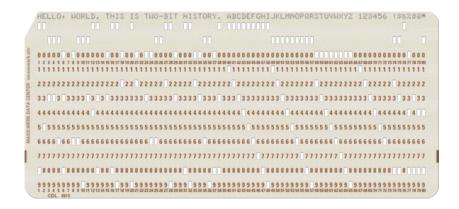

| 16. | Tarjeta perforada                                        | 50 |

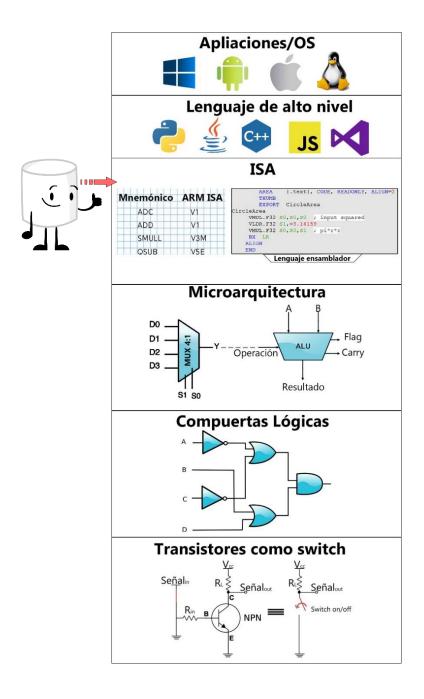

| 17. | Jerarquía de las computadoras                            | 54 |

| 18. | Regiones de operación del transistor                     | 55 |

| 19. | Representación del sistema decimal                       | 57 |

| 20. | Representación del sistema binario                       | 57 |

| 21. | Representación del sistema hexadecimal                   | 58 |

| 22. | Sistema decimal, binario y hexadecimal                   | 59 |

| 23. | Equipos Ulink                                            | 60 |

|     |                                                          |    |

| 24. | Versiones de MDK disponibles para descargar         | 61 |

|-----|-----------------------------------------------------|----|

| 25. | Diagrama del funcionamiento de Keil® MDK-ARM        | 63 |

| 26. | Página web de Keil versión 4                        | 66 |

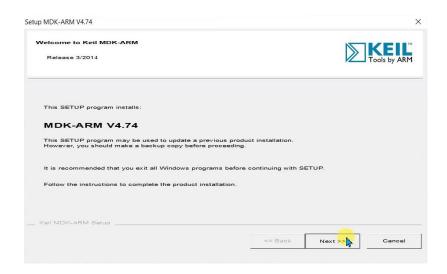

| 27. | Wizard de instalación                               | 67 |

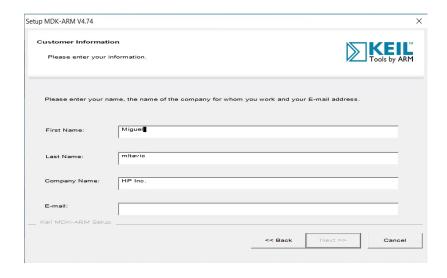

| 28. | Formulario de datos de usuario                      | 67 |

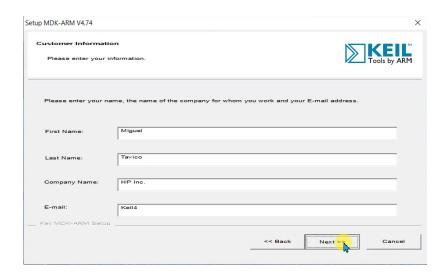

| 29. | Formulario completo de usuario                      | 68 |

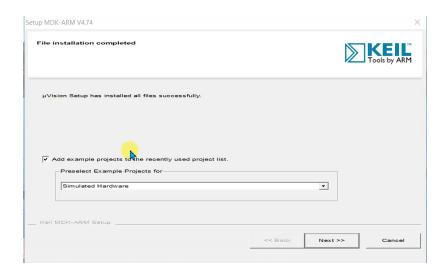

| 30. | Agregar ejemplos básicos en Keil                    | 68 |

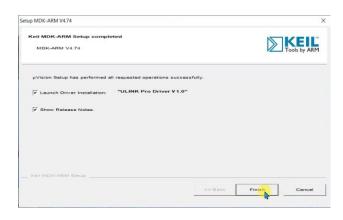

| 31. | Finalizar instalación de Keil uVision® 4            | 69 |

| 32. | Keil uVision® 4 instalado correctamente             | 69 |

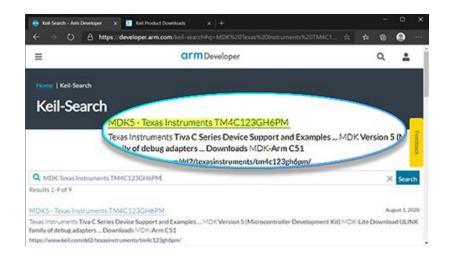

| 33. | Búsqueda de Keil uVision® 5                         | 70 |

| 34. | Selección de MDK5 -Texas Instruments para descargar | 71 |

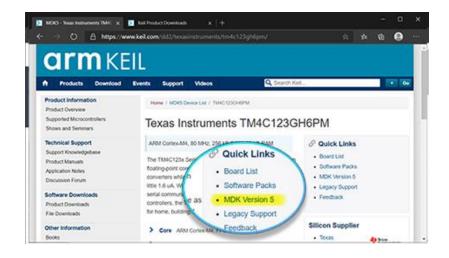

| 35. | Selección de MDK versión 5 para descargar           | 71 |

| 36. | Descarga de MDK v5                                  | 72 |

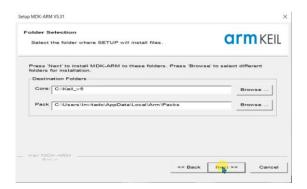

| 37. | Selección de ruta para instalar Keil uVision® 5     | 72 |

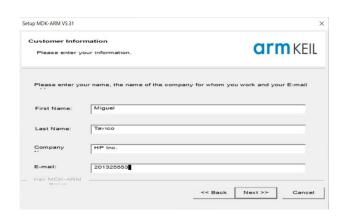

| 38. | Formulario de datos de usuario                      | 73 |

| 39. | Instalación de Ulink Drivers                        | 73 |

| 40. | Keil uVision® 5 instalado correctamente             | 74 |

| 41. | Instalación de paquetes en Keil uVision®5           | 75 |

| 42. | Búsqueda de paquetes para Tiva C Series             | 76 |

| 43. | Selección del paquete TM4C123x Series               | 76 |

| 44. | Instalación de Keil::TM4C_DFP                       | 77 |

| 45. | Página oficial de Texas Instruments                 | 78 |

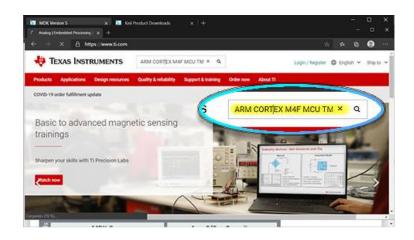

| 46. | Búsqueda de ARM CORTEX                              | 78 |

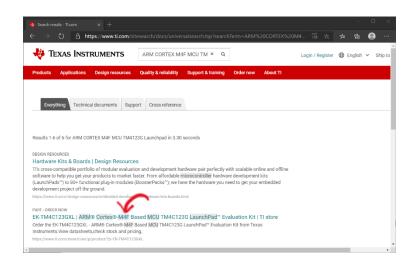

| 47. | Búsqueda del software para ARM CORTEX               | 79 |

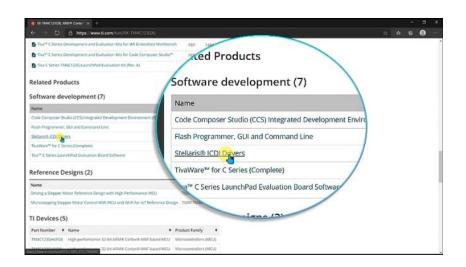

| 48. | Búsqueda de Stellaris® ICDI Drivers                 | 80 |

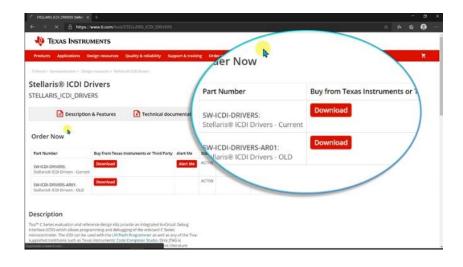

| 49. | Descarga de Stellaris® ICDI Drivers                 | 80 |

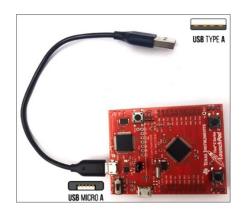

| 50. | Conexión del cable USB A                            | 81 |

| 51. | Conexión del cable USB en la Tiva C                 | 81 |

| 52  | Conexión Tiva C y computadora                       | 82 |

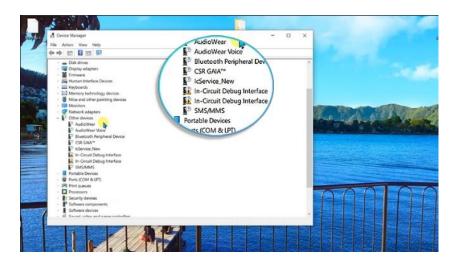

| 53. | Device Manager de Windows                                  | 83  |

|-----|------------------------------------------------------------|-----|

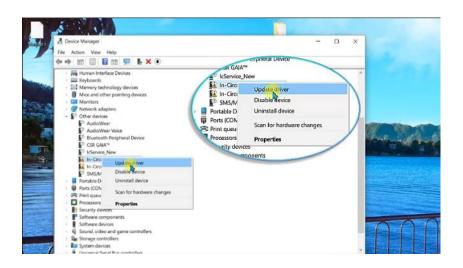

| 54. | Update Drivers en Device Manager                           | 83  |

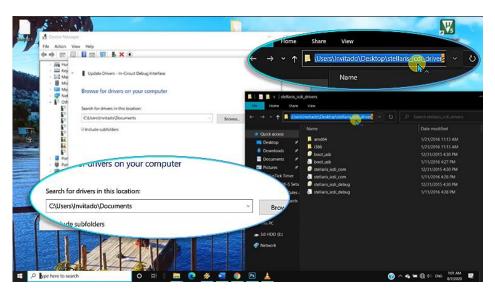

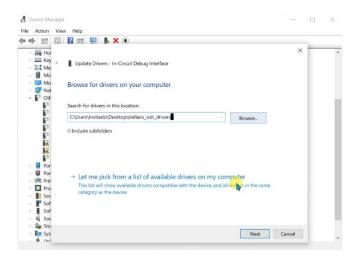

| 55. | Ubicación de los drivers dentro de Windows                 | 84  |

| 56. | Selección de la ubicación de los drivers                   | 84  |

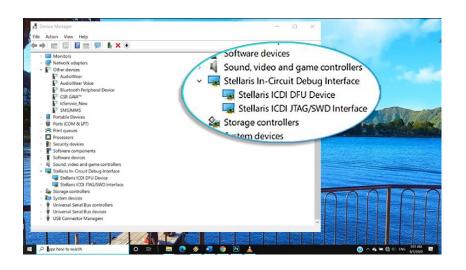

| 57. | Actualización exitosa de drivers para Stellaris® ICDI      | 85  |

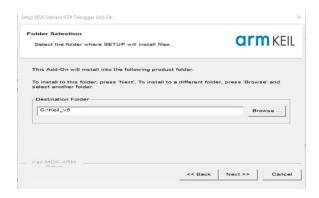

| 58. | Búsqueda de Stellaris® ICDI Debug Adapter Support          | 86  |

| 59. | Instalación de Stellaris® ICDI Debug Adapter Support       | 86  |

| 60. | Verificación de la correcta instalación de Stellaris® ICDI | 87  |

| 61. | Banco de registros del núcleo                              | 90  |

| 62. | Registros APSR, EPSR e IPSR                                | 94  |

| 63. | Bits dentro del registro xPSR                              | 94  |

| 64. | Registro xPSR                                              | 95  |

| 65. | Acceso al registro PSR                                     | 95  |

| 66. | Acceso individual al registro PSR                          | 95  |

| 67. | Campos para utilizar en assembler                          | 96  |

| 68. | Sintaxis en lenguaje ensamblador                           | 97  |

| 69. | Sintaxis de código                                         | 98  |

| 70. | Implementación de sintaxis en assembler                    | 98  |

| 71. | Instrucción LDR Y MOV                                      | 99  |

| 72. | Uso de las instrucciones LDR y STR                         | 99  |

| 73. | Datos en programa                                          | 100 |

| 74. | Ejemplo de código con UAL y pre-UAL                        | 106 |

| 75. | Valor de 32 bit en R0                                      | 109 |

| 76. | Carga y descarga de la Pila mediante PUSH y POP            | 112 |

| 77. | Instrucción POP y PUSH                                     | 113 |

| 78. | Variantes de la instrucción ADD                            | 115 |

| 79. | Ejemplo de uso instrucciones de salto                      | 122 |

| 80. | Ejemplo de CBZ en código C                                 | 124 |

| 81  | Fiemplo de la instrucción CB7                              | 124 |

| 82. | Ejemplo de CBNZ en Java                             | 125 |

|-----|-----------------------------------------------------|-----|

| 83. | Ejemplo de la instrucción CNBZ                      | 125 |

| 84. | Ejemplo del uso de NOP                              | 126 |

| 85. | Datos SIMD posibles en un registro de 32 bits       | 127 |

| 86. | Diagrama del procesador Cortex®-M4                  | 128 |

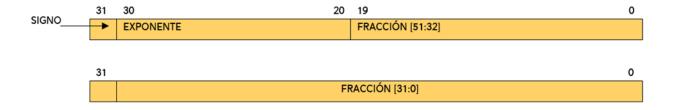

| 87. | Formato de datos de precisión simple                | 129 |

| 88. | Formato normalizado para datos con precisión simple | 129 |

| 89. | Formato de datos de precisión media                 | 130 |

| 90. | Formato normalizado para datos de precisión media   | 131 |

| 91. | Formato de datos de precisión doble                 | 131 |

| 92. | Formato normalizado para datos con precisión doble  | 132 |

| 93. | Concepto de pipeline en coprocesador                | 134 |

| 94. | Registro de control de acceso al coprocesador       | 136 |

| 95. | Configuración del registro CPACR                    | 137 |

| 96. | Registros para datos con punto flotante             | 138 |

| 97. | Bits en el registro FPSCR                           | 139 |

| 98. | Aproximaciones basadas en el estándar IEEE 754      | 144 |

| 99. | Uso de FPU en Keil MDK                              | 145 |

| 00. | Nuevo Proyecto                                      | 147 |

| 01. | Selección del nombre de archivo                     | 148 |

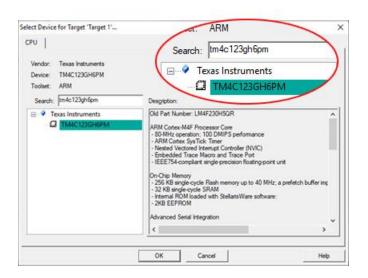

| 02. | Selección de CPU                                    | 149 |

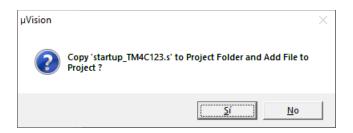

| 03. | Copiar archivo Startup                              | 149 |

| 04. | Nuevo ítem                                          | 150 |

| 05. | Nuevo ítem al grupo                                 | 151 |

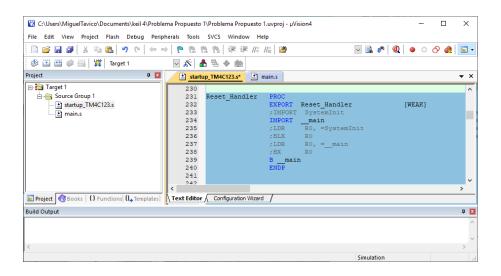

| 06. | Archivo Startup                                     | 152 |

| 07. | Opción llamada <i>Target</i>                        | 152 |

| 08. | Selección de Use Micro Lib                          | 153 |

| 09. | Selección de Use Simulator                          | 153 |

| 10  | Rebuild                                             | 154 |

| 111. | Debug                                 | 155 |

|------|---------------------------------------|-----|

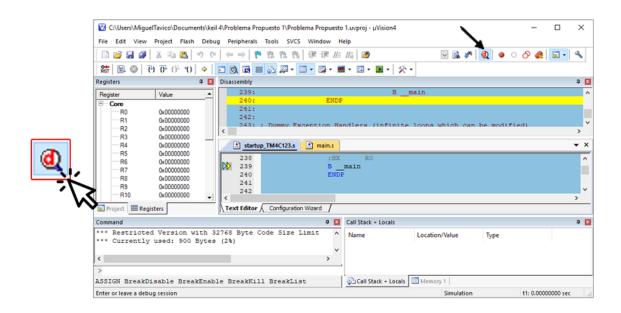

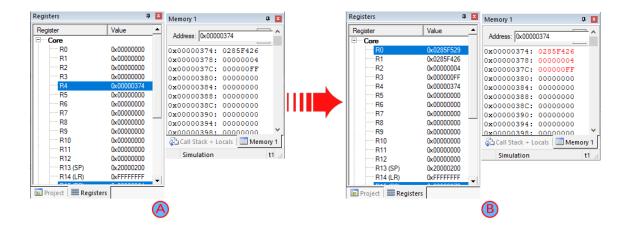

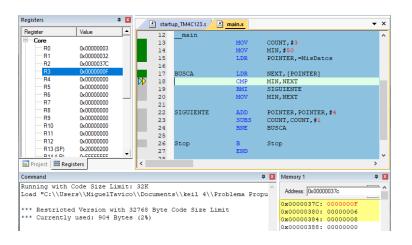

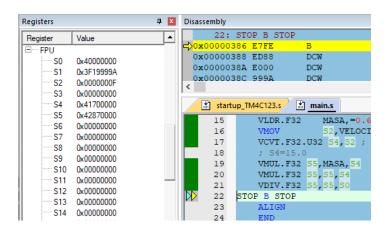

| 112. | Código fuente del problema 1          | 157 |

| 113. | Resultados del problema 1             | 158 |

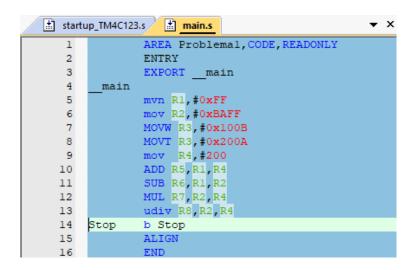

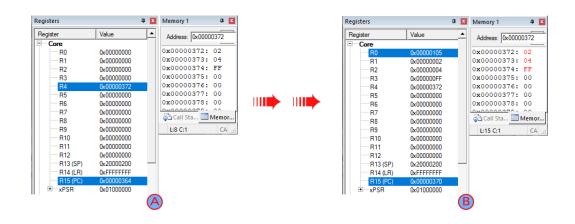

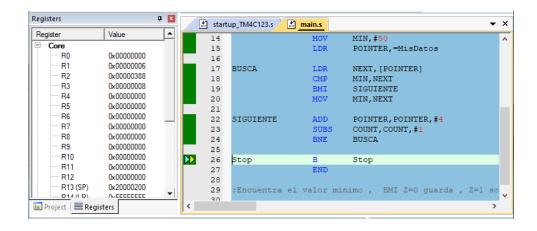

| 114. | Código fuente del problema 2          | 159 |

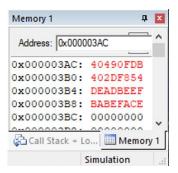

| 115. | Datos en memoria                      | 160 |

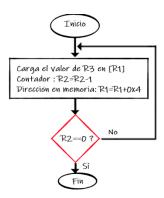

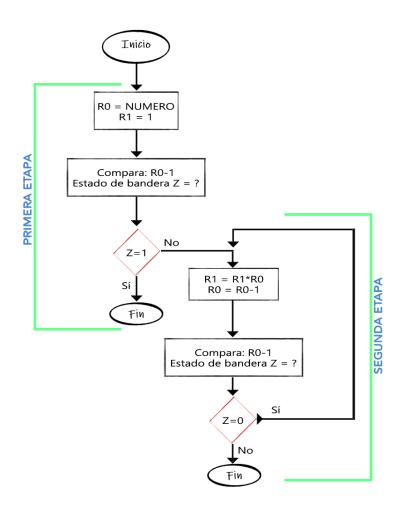

| 116. | Diagrama de flujo del problema 3      | 162 |

| 117. | Código fuente del problema 3          | 162 |

| 118. | Resultado del problema 3              | 164 |

| 119. | Diagrama de flujo del problema 4      | 166 |

| 120. | Código fuente del problema 4          | 166 |

| 121. | Resultado del problema 4              | 167 |

| 122. | Ecuación propuesta del problema 5     | 168 |

| 123. | Código fuente del problema 5          | 168 |

| 124. | Resultados del problema 5             | 169 |

| 125. | Ecuación propuesta del problema 6     | 170 |

| 126. | Código fuente del problema 6          | 171 |

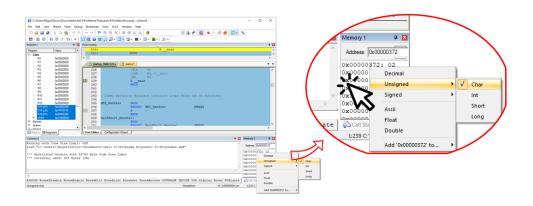

| 127. | Cambio de vista de la memoria         | 172 |

| 128. | Resultados del problema 6             | 172 |

| 129. | Código fuente del problema 7          | 174 |

| 130. | Resultado del problema 7              | 176 |

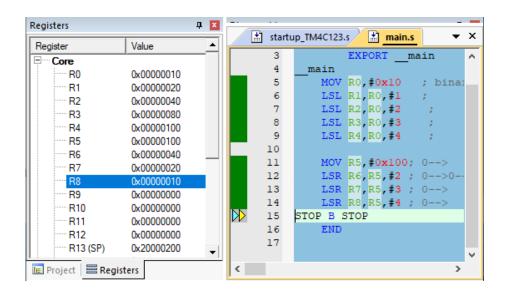

| 131. | LSL y LSR                             | 177 |

| 132. | Multiplicación indirecta con LSL      | 178 |

| 133. | División indirecta con LSR            | 178 |

| 134. | Código fuente del problema 8          | 179 |

| 135. | Resultados del problema 8             | 180 |

| 136. | Resultados matemáticos del problema 8 | 180 |

| 137. | Diagrama de flujo del problema 9      | 183 |

| 138. | Código fuente del problema 9          | 184 |

| 139. | Valores en memoria del problema 9     | 185 |

| 140. | Resultado del problema 9                 | 185 |

|------|------------------------------------------|-----|

| 141. | Factorial de un número                   | 186 |

| 142. | Diagrama de flujo del problema 10        | 187 |

| 143. | Código fuente del problema 10            | 188 |

| 144. | Resultado del problema 10                | 189 |

| 145. | Configuración del registro CPACR         | 190 |

| 146. | Código fuente del problema 11            | 191 |

| 147. | Valores dentro de FPU                    | 192 |

| 148. | Resultados del problema 11               | 193 |

| 149. | Código fuente del problema 12            | 194 |

| 150. | Valores cargados en los registros        | 195 |

| 151. | Valores cargados en memoria              | 195 |

| 152. | Manipulación de valores en los registros | 196 |

| 153. | Resultado del problema 12                | 197 |

| 154. | Energía cinética                         | 197 |

| 155. | Código fuente del problema 13            | 198 |

| 156. | Conversión a decimal                     | 199 |

| 157. | Resultado del problema 13                | 200 |

| 158. | Perímetro de un círculo                  | 200 |

| 159. | Código fuente del problema 14            | 201 |

| 160. | Valores almacenados en registros         | 202 |

| 161. | Resultado del problema 14                | 203 |

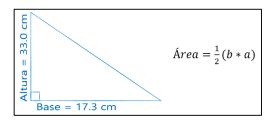

| 162. | Área de un triángulo rectángulo          | 204 |

| 163. | Código fuente del problema 15            | 205 |

| 164. | Resultado del problema 15                | 206 |

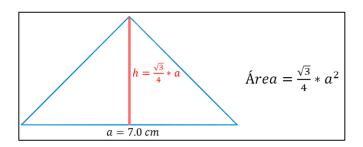

| 165. | Área de un triángulo equilátero          | 207 |

| 166. | Código fuente del problema 16            | 208 |

| 167. | Solución del problema 16                 | 209 |

| 168. | Diagrama de flujo del problema 17        | 211 |

| 169.   | Código fuente del problema 17                           | 213 |

|--------|---------------------------------------------------------|-----|

| 170.   | Datos del problema 17                                   | 214 |

| 171.   | Resultado del problema 17                               | 215 |

| 172.   | Aproximación de Sen(x)                                  | 216 |

| 173.   | Aproximación de Sen(x) con n = 3                        | 217 |

| 174.   | Código fuente del problema 18                           | 218 |

| 175.   | Resultado del problema 18                               | 219 |

|        | TABLAS                                                  |     |

| l.     | Criterios del aprendizaje                               | 3   |

| II.    | Diferencia entre el racionalismo y empirismo            | 6   |

| III.   | Unidades de medidas en los procesadores                 | 30  |

| IV.    | Rango de memorias para procesadores Cortex M3 y M4      | 35  |

| V.     | Interfaces de bus en procesadores Cortex® M3 y M4       | 47  |

| VI.    | Representación de mnemónicos para Intel i386            | 51  |

| VII.   | Directivas para insertar datos en programa              | 101 |

| VIII.  | Directivas importantes                                  | 102 |

| IX.    | Sufijos para leguaje ensamblador para Cortex®-M         | 105 |

| X.     | Instrucciones para transferencia de datos               | 107 |

| XI.    | Transferir datos entre la FPU y los registros centrales | 108 |

| XII.   | Instrucciones de acceso a memoria                       | 110 |

| XIII.  | PUSH y POP                                              | 111 |

| XIV.   | VPUSH y VPOP                                            | 114 |

| XV.    | Instrucciones para operaciones aritméticas              | 116 |

| XVI.   | Instrucciones para multiplicar y MAC                    | 117 |

| XVII.  | Instrucciones para álgebra booleanas                    | 118 |

| KVIII. | Instrucciones de prueba y compara                       | 119 |

| XIX    | Instrucciones de salto sin condición                    | 120 |

| XX.      | Estado de los bits de las banderas del registro APSR | 121 |

|----------|------------------------------------------------------|-----|

| XXI.     | Instrucciones para salto condicionado                | 121 |

| XXII.    | Sufijos condicionales                                | 122 |

| XXIII.   | Instrucción para llamar o invocar a una función      | 123 |

| XXIV.    | Instrucciones de multiplicación y MAC                | 127 |

| XXV.     | Ejemplo para valores con punto flotante              | 130 |

| XXVI.    | Registros FPU adicionales                            | 135 |

| XXVII.   | Configuración CP10 y CP11                            | 136 |

| XXVIII.  | Descripción de bits en FPSCR                         | 139 |

| XXIX.    | Banderas N, Z, C, y V dentro de FPSCR                | 141 |

| XXX.     | Operaciones para datos con punto flotante            | 141 |

| XXXI.    | Valores para operar                                  | 155 |

| XXXII.   | Operaciones matemáticas                              | 156 |

| XXXIII.  | Dirección en memoria                                 | 159 |

| XXXIV.   | Dirección y valor                                    | 161 |

| XXXV.    | Valores propuestos                                   | 165 |

| XXXVI.   | Registros y valores del problema 7                   | 173 |

| XXXVII.  | Banderas del registro xPSR                           | 174 |

| XXXVIII. | Valores del problema 9                               | 181 |

| XXXIX.   | Registros renombrados con RN                         | 181 |

| XL.      | Valores para problema 11                             | 190 |

| XLI.     | Vueltas v tiempos                                    | 210 |

# LISTA DE SÍMBOLOS

| Símbolo | Significado                 |

|---------|-----------------------------|

| cm      | Centímetro                  |

| 1       | División                    |

| Ghz     | Gigahertz                   |

| Hz      | Hertz                       |

| =       | Igualdad                    |

| J       | Julios                      |

| Kg      | Kilogramos                  |

| С       | Lenguaje de programación    |

| Mhz     | Megahertz                   |

| *       | Multiplicación              |

| -       | Resta                       |

| S       | Segundos                    |

| +       | Suma                        |

| ®       | Símbolo de marca registrada |

| Vi      | Valor inmediato             |

### **GLOSARIO**

AND Operación lógica en donde el resultado es 1 si solo si

todas las entradas también son 1 de lo contrario el

resultado es 0.

ARM Arquitectura de procesadores tipo RISC de 32 bits o

64 bits.

Bit Unidad básica para el campo de las computadoras y

comunicaciones, el cual puede tener dos valores cero

o uno.

Bus Sistema digital para transferir datos entre

componentes o dispositivos electrónicos, compuesto

por un conjunto de cables o pistas en un circuito.

**CMC** Cualquier tipo de comunicación entre personas

mediante el uso de dos o más dispositivos

electrónicos.

Compilador Software o programa que traduce un código fuente

escrito en un lenguaje de alto nivel a un lenguaje de

bajo nivel.

**DSP** Sistema basado en un microprocesador especializado

para procesar señales digitales.

Educación Disciplina que se basa en analizar los métodos de

enseñanza para la adquisición de conocimiento.

IEEE El Instituto de Ingenieros electrónicos y eléctricos es

una asociación encargada de normalizar nuevas

tecnologías y protocolos de comunicación.

Lenguaje de máquina Sistema de código directamente interpretable por un

microprocesador conformado por unos y ceros.

Memoria Flash Memoria eléctricamente programable, este tipo de

memoria no volátil.

Memoria RAM Memoria de acceso aleatorio de tipo volátil, es

utilizada cuando la velocidad de acceso a la

información es muy importante.

Memoria ROM Memoria de solo lectura, este tipo de memoria es no

volátil.

MMU Circuitos integrados encargados de manejar el acceso

a la memoria.

MPU Unidad de protección de memoria, permite definir

rangos con diferentes permisos y puede leer

información de fallas.

NOT Operación lógica la cual da como resultado el valor

invertido de la entrada.

OR Operación lógica en la cual el resultado es 1 si solo si

una de las entradas es 1 de lo contrario el resultado

es 0.

Saturación Estado de un circuito electrónico en donde la magnitud

de voltaje de salida posee una tención próxima a la

fuente con la que se está alimentado.

Sensores Dispositivo electrónico capaz de detectar magnitudes

físicas o químicas e interpretarlas de forma digital.

SIMD Componentes electrónicos capaces de operar

múltiples datos de forma paralela al mismo tiempo.

**USB** Bus de comunicación con interfaz de 4 cables que

interconectan dispositivos electrónicos con una

computadora.

#### RESUMEN

El presente trabajo de graduación brinda material digital bajo el modelo constructivista de educación para el curso de Electrónica 5 de la Facultad de Ingeniería de la Universidad de San Carlos de Guatemala, en la Escuela de Ingeniería Mecánica Eléctrica. Se estudian los inicios del lenguaje ensamblador, así como su correcta implementación en los procesadores de la familia Cortex®-M.

En el primer capítulo se estudia el aprendizaje en la educación, se explica cómo las personas mediante el constructivismo van aprendiendo y construyen su propio conocimiento. Además, se habla sobre la importancia de las TICs para brindar educación de calidad a distancia. El segundo capítulo explica los inicios del lenguaje de programación ensamblador y expone a la familia de procesadores llamados Cortex, los cuales pueden ser programados en ensamblador. Se explica la correcta instalación del software de desarrollo Keil® MDK, en el cual será utilizado para programar el procesador Cortex®-MF.

En el tercer capítulo se enuncian todas las características internas del procesador Cortex®-M, como lo son: registros, Pila, sintaxis, directivas, set de instrucciones para valores enteros y decimales. El cuarto y último capítulo se proponen y resuelven varios ejemplos en lenguaje ensamblador, esto con la finalidad de que el lector pueda comprender totalmente el uso del lenguaje.

### **OBJETIVOS**

#### General

Diseñar e implementar material digital bajo el modelo constructivista en la educación para el curso de Electrónica 5.

## **Específicos**

- 1. Explicar claramente el uso del constructivismo para adquirir nuevo conocimiento.

- 2. Conocer los inicios del lenguaje ensamblador.

- 3. Presentar la familia de procesadores Cortex®-M así como su arquitectura.

- 4. Explicar el uso correcto de las instrucciones, directivas, registros, operaciones y saltos en el lenguaje ensamblador utilizando Keil® uVision MDK.

- Diseñar varios problemas para ser resueltos en el lenguaje ensamblador utilizando el microcontrolador TM4C123GH6PM.

# INTRODUCCIÓN

Con el avance de la tecnología los dispositivos electrónicos han disminuido de tamaño y aumentado su velocidad de procesamiento. Todos los dispositivos electrónicos necesitan de un procesador, como los procesadores de la familia Cortex. La familia de procesadores Cortex son de alto rendimiento, bajo consumo energético y fáciles de programar en lenguaje ensamblador.

Arm Holdings es una compañía la cual lejos de producir masivamente procesadores sólo se encarga de diseñar las distintas arquitecturas de los procesadores y posteriormente vender los derechos para que otras empresas se encarguen de producirlos e implementarlos en dispositivos electrónicos

Texas Instruments implementa el Cortex®-MF dentro del microcontrolador TM4C123GH6PM. El procesador cuenta con 12 registros de propósito general y 3 registros de uso especial dentro del núcleo (con un tamaño de 32 bits). También cuenta con una unidad de punto flotante o FPU basada en el estándar IEEE 754 la cual brinda la posibilidad de poder operar datos con decimales de precisión simple. La FPU cuenta con 32 registros con un tamaño de 32 bits o al agruparlos en pares se obtiene 16 registros con tamaño de 64 bits

La jerarquía de una computadora es necesaria conocerla, esto ayuda a saber qué es lo que sucede al momento de programar en un lenguaje de bajo nivel. En el nivel llamado ISA se encuentran el conjunto de especificaciones e instrucciones necesarias para poder programar un microprocesador.

Existen varios tipos de ISAs las cuales se diferencian unas ante otras con base en la cantidad de instrucciones que posee, la longitud y cómo se procesa esa información. Dentro de las ISAs se pueden mencionar a la arquitectura CISC y RISC. Cabe resaltar que los procesadores Cortex-M se basan puramente en la arquitectura RISC

Para evitar lidiar con el lenguaje de máquina (basada en 0 y 1) se implementa el uso del lenguaje ensamblador ya que dispone de código simbólico (nemónicos) para reemplazar los largos sets de instrucciones escritos puramente con 0 y 1. Para programar el procesador Cortex®-MF se tiene que tomar en cuenta el entorno de desarrollo a usar, en qué software se va a realizar el código. Para el presente trabajo se estará trabajando con Keil® MDK-Lite.

# 1. APRENDIZAJE EN LA EDUCACIÓN

La educación consiste en una disciplina que analiza los métodos de enseñanza y facilita el aprendizaje o la adquisición de conocimiento. Por otro lado, el aprendizaje causa un cambio en la forma de ser o pensar de la persona en función de la experiencia individual o grupal. El término aprendizaje y educación se ha utilizado como sinónimo lo cual es incorrecto, son procesos completamente distintos.

Una buena educación en la persona depende plenamente de un buen aprendizaje. Actualmente, se tienen problemas respecto a la educación sin un aprendizaje, en donde sólo se hace repetir y memorizar al estudiante. El problema anterior también está presente en la educación superior en donde lo enseñado no tiene relación con lo que se encuentra en el ámbito laboral.

Aunque se logre memorizar todo el contenido o temas de estudio requeridos no es suficiente, no se trata de aprender sino también de aprender a aprender y razonar lo aprendido. Se necesita comprender que el aprendizaje no es algo impuesto y romper el paradigma de que el estudiante no puede aprender o enseñar por sí solo, sólo hay que tener en cuenta que la educación siempre tiene que ir acompañada de la supervisión de un docente o tutor o un trabajo constante por parte del estudiante.

#### 1.1. La educación

La educación nos concierna a todos desde el momento de nacer. El término "educación" puede tener distinta interpretación, se puede decir que es el proceso de facilitar la adquisición de nuevos conocimientos, sin embargo, la educación puede ocurrir indirectamente sin ninguna ayuda externa. La educación inicia desde el momento en que nuestro cerebro empieza a retener información y la empieza a asociar con acciones. Conceptualmente se usa con frecuencia el vocablo para otorgar un significado a acontecimientos que se relacionan con lo educativo.

El ser humano basa su desarrollo social y psicológico en la educación, la educación brinda un incesante aprendizaje también llamado proceso de Humanización. Este proceso brinda a las personas cualidades de ser empáticas, afectivas, amorosas, racionales y comunicativas. García Carrasco (1987), destaca el hecho de que la educación no se refiere a una actividad más bien a un conjunto de ella.

Brindar una definición muy precisa del significado del término "Educación" es muy complicado, por tal se procederá a establecer límites para poder establecer un significado correcto. Se describe las características más sobresalientes que logran conformar el término "Educación":

- La humanización, acción y efecto por la cual las personas se dotan de cualidades humanas, estas ayudan a una persona a tener actitudes relevantes.

- Los elementos básicos de la educación:

- Emisor, persona que brinda nuevo conocimiento, puede ser pasivo o activo.

- Receptor, persona que recibe o capta la información de forma directa o indirecta.

La acción brindada por el educador y el educando en una situación educativa. La enseñanza brindada es de forma sistematizada y gradual. El aprendizaje se estudia mediante la manipulación, la interacción y la formación.

## 1.1.1. Enseñanza y Aprendizaje

La enseñanza dentro del constructivismo puede ser implementada mediante distintos métodos, en los cuales el estudiante logra adquirir nuevo conocimiento de forma correcta. Ahora bien, el término aprendizaje difiere en su significado dependiendo del punto de vista, ya que no existe una definición plenamente aceptada por todos los teóricos, investigadores, pedagogos y otros profesionales.

## 1.1.1.1. Teorías del aprendizaje

Una definición básica para el término aprendizaje es:

"Adquisición del conocimiento de algo por medio del estudio, el ejercicio o la experiencia, en especial de los conocimientos necesarios para aprender algún arte u oficio."

Tabla I. Criterios del aprendizaje

| 1.° | El aprendizaje implica un cambio en la forma de ser y |  |

|-----|-------------------------------------------------------|--|

|     | actuar                                                |  |

| 2.° | El aprendizaje es adquirir y compartir conocimientos  |  |

| 3.° | El aprendizaje puede ocurrir mediante varios métodos  |  |

Fuente: elaboración propia, empleando Microsoft Word.

<sup>&</sup>lt;sup>1</sup> EDU GESTORES. *Conocimiento y Aprendizaje*. 2017. https://www.edugestores.pe/docs/conocimiento-y-aprendizaje/history/?revision=14025. Consulta: 1 de enero de 2020.

El aprendizaje conlleva un cambio en la forma de ser de una persona. Las personas aprenden cuando adquieren nuevo conocimiento y logran realizar distintas actividades lógicas y físicas de distinta manera, de una forma más eficiente.

El aprendizaje es inferencial, la persona aprende y comprende nuevos conocimientos sin darse cuenta. Al obtener nuevo conocimiento el aprendizaje en las personas inicia, luego del aprendizaje estas personas adquieren nuevas habilidades, nuevos conocimientos, creencias o conductas las cuales no se perciben inmediatamente.

Un segundo criterio consiste en adquirir nuevo conocimiento, independientemente de la forma en que se obtuvo el nuevo conocimiento las personas logran transmitir lo ya aprendido hacia otras personas. Compartir el conocimiento de una persona a otra puede ser por distintos medios.

Un tercer criterio es el aprendizaje mediante la experiencia. Esto se logra obtener mediante la práctica o al observar algún evento que ocurra a su alrededor. Lo anterior cambia la forma de ser y pensar de la persona.

El aprendizaje permite a la persona construir su propio pensamiento mediante su propia experiencia, le brinda nuevas habilidades y logra mejorar sus valores como persona. Algunos de los beneficios del aprendizaje mediante la experiencia son:

- Permite un crecimiento personal a partir del conocimiento previo

- Mejora la estructura cognitiva del estudiante

- Ayuda a mejorar las actitudes de la persona de manera positiva

- Permite enfocar el aprendizaje

## 1.2. Precursores de las teorías modernas del aprendizaje

El origen de la teoría y postulado del aprendizaje se remontan a varios años. Muchos temas o problemas que se estudian hoy en día no son nuevos. Entre los orígenes de las teorías contemporáneas del aprendizaje, las posturas filosóficas sobre el origen del conocimiento y su aprendizaje se puede mencionar lo siguiente.

## 1.2.1. Teoría del aprendizaje

Desde el punto de vista filosófico, el aprendizaje podría definirse con el término epistemología. Esta es la parte de la filosofía encargada de estudiar los principios de la naturaleza y métodos del conocimiento humano, así como el origen de ese conocimiento.

El racionalismo como el empirismo son las posturas que intentan explicar la forma en que las personas adquieren conocimiento, tanto el racionalismo como el empirismo tienen fundamentos filosóficos opuestos.

En la tabla II, se brinda una breve explicación de las diferencias entre el racionalismo y el empirismo.

Tabla II. Diferencia entre el racionalismo y empirismo

|                  | Racionalismo             | Empirismo                  |

|------------------|--------------------------|----------------------------|

| Base fundamental | La razón es la base del  | La experiencia es la base  |

|                  | conocimiento humano      | del conocimiento           |

| Ideas            | Las personas poseen      | Las personas no poseen     |

|                  | conocimiento innato      | conocimiento innato        |

| El conocimiento  | Se obtiene de la razón y | Se obtiene de la           |

|                  | lógica propia de cada    | experiencia y en la propia |

|                  | persona                  | experimentación durante    |

|                  |                          | la vida de la persona.     |

Fuente: elaboración propia, empleando Microsoft Word.

#### 1.2.2. Racionalismo

Postura filosófica que defiende lo que se debe conocer de la verdad, para poder tener la razón. La razón es la generadora del conocimiento lo cual es innato del ser, los individuos al nacer ya poseen determinados conocimientos. La mente logra percibir el mundo exterior mediante los sentidos y los manipula con leyes innatas. La persona aprende del mundo mediante su propia percepción, por esa razón no se tiene un conocimiento absoluto. El conocimiento es empírico ya que la información se toma del mundo exterior y la mente posteriormente lo interpreta. Por lo anterior se puede decir que el conocimiento surge mediante lo que percibe la mente, las ideas se generan en función de la mente.

## 1.2.3. Empirismo

En contraste con el racionalismo, el empirismo se basa en que la única fuente de conocimiento es mediante la experiencia y niega totalmente la idea innata del racionalismo.

La experiencia puede ser interna o externa, por esa razón se puede decir que es producto de los sentidos. De acuerdo con el empirismo la base, origen y límite del conocimiento es la experiencia. Se puede resumir como corriente filosófica basada en la práctica, experiencia y en la observación de los hechos.

#### 1.3. El constructivismo en la educación como método de enseñanza

El constructivismo es una postura psicológica y pedagógica. Existen varias teorías las cuales son las bases del constructivismo, esas teorías fueron postuladas por Piaget, Vygotsky y Ausubel. Lo publicado por cada autor no se denomina postulado totalmente constructivista pero sus ideas son las guías de una corriente puramente constructivista.

## 1.3.1. Jean Piaget

Jean William Fritz Piaget fue un epistemólogo y biólogo suizo, se dedicó al estudio y análisis de las respuestas erróneas las cuales son comunes en las personas al momento del desarrollo del conocimiento, estudió la razón de esas respuestas "erróneas". Para Piaget no importa la autoridad sobre el estudiante durante su interacción, se interesa sencillamente en saber por qué ellos piensan de la forma en que lo hacen ya sea un pensamiento correcto o erróneo.

Piaget reinventa la Psicología del Desarrollo, ese Desarrollo no es más que una adicción del nuevo conocimiento. Las etapas para obtener un nuevo conocimiento suceden ante conflictos, accidentes y eventos importantes en la vida de la persona. El estudiante en cada etapa elabora teorías acerca del mundo circundante sin importar su veracidad.

## 1.3.1.1. El origen del pensamiento humano

Piaget estudiaba cómo surge el pensamiento en los niños, estaba convencido de que el modo en que evoluciona el pensamiento infantil servía para comprender el pensamiento racional en su estado más puro, el cual es el pensamiento científico. Piaget habla sobre la utilidad de la comprensión del pensamiento racional como resultado de una evolución. Él acumuló pruebas que sostienen un nuevo modo de comprender la evolución de la inteligencia, el proceso del desarrollo y cómo se va construyendo el conocimiento es llamado constructivismo.

Piaget demostró que la actividad psíquica del niño no es totalmente gráfica, demostró que nociones tan simples como el espacio, casualidad y otros eventos eran resultado de las experiencias adquiridas por el niño en los primeros años de su vida.

Para Piaget la inteligencia y capacidad para aprender se encuentra ligado al medio físico y social al que el niño o niña esté expuesto. La lógica es base fundamental para el entendimiento y la capacidad cognitiva, la cual se desarrolla en los primeros días de vida y continúa paulatinamente con el transcurrir de los años.

## 1.3.2. Lev Vygotsky

Lev Semiónovich Vygotsky fue un psicólogo, fundador de la psicología histórico-cultural y precursor de la neuropsicología soviética. Vygotsky plantea su modelo de aprendizaje sociocultural, sostiene que los eventos socioculturales proporcionan nuevos conocimientos. Se explica el aprendizaje como una forma de socialización. El conocimiento es causa del desarrollo cultural.

El concepto básico es la zona de desarrollo próximo (ZDP) en la cual cada estudiante es capaz de aprender una serie de habilidades o nuevas formas de pensar lo cual se basa en su nivel de desarrollo, pero existen otros conceptos o habilidades que pueden ser comprendidos mediante la ayuda de adultos. En resumen, lo que el estudiante puede aprender por sí solo y con ayuda de otros se le conoce como ZDP. En este postulado el catedrático tiene un papel muy importante en el desarrollo de las estructuras mentales debido a que facilita el aprendizaje hacía en el estudiante, el estudiante logra construir conocimiento mucho más complejo.

Para Vygotsky existen dos tipos de funciones mentales: inferiores y superiores. Las inferiores son las funciones mentales con las que se nace y están determinadas genéticamente. Las funciones mentales superiores se adquieren y desarrollan a través de la interacción sociocultural, estas funciones están determinadas por la forma de ser de la sociedad en la que el estudiante se encuentra involucrado.

#### 1.3.2.1. Método de enseñanza

Los estudiantes se colocan en situaciones en las cuales su mente se ve forzada a atender el problema, los estudiantes disponen del apoyo de otros compañeros o catedráticos. Se toma mucho en cuenta otro estudiante porque puede ser que recién haya resuelto el problema y será más sencillo explicar la solución. Los profesionales deben guiar a los estudiantes con explicaciones, demostraciones, ejemplos similares y demás.

#### 1.3.3. David Ausubel

David Paul Ausubel fue un psicólogo y pedagogo de gran importancia para el constructivismo, su teoría es cognitiva. Ausubel ponía mucho énfasis en la enseñanza la cual según él se logra a partir de los conocimientos que ya posee el alumno. Por lo anterior el primer paso para garantizar un buen aprendizaje es averiguar lo que el estudiante ya sabe.

Aprendizaje significativo se le llama al momento en el cual la información adquiere un significado comprensible para el estudiante a través de la asociación de conceptos existentes en su memoria. "La teoría de la Asimilación" permite comprender claramente el aprendizaje significativo, ayuda a comprender cómo los nuevos conocimientos se integran a los existentes. La asimilación ocurre cuando una nueva información logra ser integrada al conocimiento, se genera una asociación entre ellas, y esa asociación permite expandir el conocimiento antiguo.

Una de las ventajas del aprendizaje significativo implica una construcción del conocimiento intencional, por esa razón la información aprendida significativamente será asociada y retenida más tiempo en la mente del estudiante. El conjunto de conceptos adquiridos por el estudiante en la estructura cognitiva será único. Aunque se haya usado la misma tarea de aprendizaje cada persona asociara a su propia manera el nuevo conocimiento.

## 1.3.4. ¿Qué es el constructivismo?

No existe una única definición del término constructivismo, el término no es una teoría sino una epistemología o explicación filosófica acerca de la naturaleza del aprendizaje. en concreto propone que las personas crean o van construyendo su propio conocimiento.

Hay muchas verdades, pero ninguna debe ser considerada más correcta que las otras. El constructivismo no propone que existan principios del aprendizaje que se deban descubrir y poner a prueba, sino que las personas crean su propio aprendizaje.

Los principales exponentes constructivistas rechazan la idea de que existan verdades científicas absolutas, ya que se espera el descubrimiento y la verificación. Ninguna afirmación se puede considerar como verdadera. En lugar de considerar el conocimiento como verdadero, los constructivistas lo definen como una hipóstasis de trabajo el cual da inicio cuando los seres humanos empiezan a adquirir conocimiento.

El conocimiento no inicia de forma externa ante una persona, sino que se genera dentro de ellas. La construcción de ese conocimiento para una persona es plenamente verdadera, pero no necesariamente para los demás. Lo anterior debido a que cada persona construye su conocimiento con base en sus creencias y experiencias, entonces todo el conocimiento es subjetivo y personal.

# 1.4. Aspectos básicos según Piaget, Vygotsky y Ausubel

Los aspectos más relevantes del constructivismo según los autores son:

## Piaget

Reinventa la Psicología del Desarrollo, ese desarrollo se da mediante la adición de nuevo conocimiento. Para que las personas logren adquirir nuevo

conocimiento debe existir conflictos, accidentes o eventos importantes en la vida de ellas.

## Vygotsky

Enuncia el aprendizaje sociocultural, eventos socioculturales que ocurren en la vida de una persona proporcionando nuevos conocimientos. Lo que la persona puede aprender por sí solo y con ayuda de otros se conoce como ZDP. Los profesionales deben guiar a los estudiantes con explicaciones claras, demostraciones, ejemplos similares y demás.

#### David Ausubel

Basando su postulado en la experiencia, las personas estructuran el mundo a través de las percepciones de sus experiencias. La teoría de la Asimilación permite comprender claramente el aprendizaje significativo el cual ayuda a comprender cómo los nuevos conocimientos se integran a los existentes.

La asimilación ocurre cuando una nueva información se integra al antiguo conocimiento, se genera una asociación entre ellas y esa asociación permite expandir el conocimiento. Aunque se haya usado la misma tarea de aprendizaje cada persona asocia a su manera el nuevo conocimiento.

# 1.5. Ambientes de aprendizaje constructivistas

Aprender en un ambiente constructivista no quiere decir que los estudiantes pierdan el tiempo, en este tipo de ambiente se debe crear actividades y material estimulante que fomente el aprendizaje sin interrupciones.

Las aulas constructivistas se basan en los conceptos más importantes, las actividades suelen incluir fuentes de los datos y materiales extras. Los docentes interactúan con los estudiantes averiguando lo que les interesa y sus puntos de vista. La clave es estructurar el ambiente de aprendizaje de forma que los estudiantes puedan construir de una forma eficiente nuevos conocimientos y habilidades.

En una clase tradicional, durante una lección nueva, las suposiciones y las respuestas brindadas por los estudiantes pueden ser incorrectas, el catedrático debe de corregir la respuesta o pensamiento erróneo. En una enseñanza constructivista se reta a los mismos estudiantes a deducir la información correcta durante una lección.

En los ambientes de estudio constructivistas se genera un aprendizaje estructurado, significativo y profundo. Por lo anterior los exámenes de verdadero y falso no son muy objetivos para evaluar los resultados en un aprendizaje constructivista. Las evaluaciones eficaces para medir la calidad del aprendizaje del estudiante son mediante la redacción de textos sobre lo aprendido o que ellos demuestren y apliquen las nuevas habilidades adquiridas.

A las evaluaciones constructivistas no le interesa tanto las respuestas correctas ni las incorrectas sino las etapas posteriores a la emisión de las respuestas. En este tipo de evaluaciones se tienen el reto en el cual los profesores diseñen actividades que estimulen la retroalimentación del estudiante para que converjan en una respuesta correcta y que logren modificar lo aprendido en caso sea necesario.

#### 1.6. La enseñanza dentro del constructivismo

Se presentan varios escenarios en los cuales el estudiante va adquiriendo de forma eficiente nuevos conocimientos mediante el constructivismo.

#### 1.6.1. Enseñanza por el descubrimiento

Ocurre cuando el estudiante obtiene conocimientos por sí mismo. El estudiante plantea y prueba hipótesis, no solo lee y escucha lo que el catedrático expone.

El razonamiento es de tipo inductivo ya que los mismos estudiantes realizan reglas, conceptos y principios generales de lo que se está aprendiendo. Este tipo de aprendizaje también suele ser llamado aprendizaje basado en problemas, aprendizaje por indagación, aprendizaje de experiencia y aprendizaje constructivista.

La enseñanza dentro del descubrimiento plantea: preguntas, problemas o situaciones complejas. Se reta a los estudiantes a formular conjeturas y llegar a una idea o concepto totalmente correcto.

## 1.6.2. Enseñanza por indagación

Este tipo de enseñanza es un tipo de aprendizaje por descubrimiento. La meta es lograr que los estudiantes razonen y luego apliquen lo comprendido a situaciones nuevas. Este tipo de enseñanza fue diseñado para el aprendizaje individual, con algunos cambios se podrá usar en grupos pequeños de estudiantes. Un detalle muy importante con respecto a las preguntas es que éstas

deben ser planteadas por expertos en el tema y se deben realizar de acuerdo con el nivel del pensamiento del estudiante.

### 1.6.3. Aprendizaje asistido por los pares

Este tipo de enseñanza utiliza mucho los principios de la enseñanza constructivista. Los estudiantes participan de forma activa en el proceso de aprendizaje, el estudiante y profesor participan con plena libertad. En el contexto individual en el cual se desarrolla este tipo de aprendizaje los estudiantes suelen hacer muchas preguntas, preguntas que no se atreverían a hacer en grupos grandes de estudiantes. Este tipo de enseñanza fomenta la cooperación entre estudiantes y ayuda a diversificar la estructura del grupo.

# 1.6.4. Aprendizaje cooperativo

El objetivo de este tipo de aprendizaje es desarrollar la habilidad de los estudiantes para trabajar en colaboración con otros estudiantes. Se debe aplicar de forma oportuna en tareas que son demasiado extensas para un solo estudiante. Existen principios que ayudan a que los grupos cooperativos tengan éxito. Uno de los criterios o principios es formar grupos con estudiantes que puedan trabajar bien juntos y que también puedan desarrollar habilidades de cooperación.

## 1.7. Evaluar el aprendizaje

El aprendizaje no se puede observar de manera directa, se observa mediante sus productos y resultados. Los investigadores y profesionales que educan a los estudiantes podrían asumir que, si se ha aprendido, pero la única forma de garantizar el aprendizaje es mediante una evaluación de los productos y los resultados del aprendizaje.

La evaluación implica determinar la calidad del nuevo conocimiento brindado por los profesionales hacia los estudiantes. Los profesionales e investigadores desean saber si ha ocurrido un aprendizaje exitoso, para determinar lo anterior se tienen varios métodos aparte de las pruebas escritas, con las cuales es posible obtener evidencia de la calidad del aprendizaje adquirido por el estudiante. Lo que se evalúa en las pruebas son las nuevas habilidades o nuevos interés y motivación personal. Las evaluaciones se realizan al finalizar de estudiar el contenido propuesta.